# SIMULASI ALAT BANTU PENJUALAN KARCIS KERETA API DENGAN MEMANFAATKAN MINIMUM SISTEM 8088 YANG DIHUBUNGKAN IBM PC-XT

| PER         |     | STAKAAN<br>TS |

|-------------|-----|---------------|

| Tgl. Federa |     | 22 NOV 1994   |

| Terima Dar  | 3   | H             |

| No. Agenda  | Tp. | 4736          |

RSE 621 391 6 Bud 5-1 1994

Oleh:

Busi Harijanto

NRP. 2902201596

JURUSAN TEKNIK ELEKTRO

FAKULTAS TEKNOLOGI INDUSTRI

INSTITUT TEKNOLOGI SEPULUH NOPEMBER

SURABAYA

1994

# SIMULASI ALAT BANTU PENJUALAN KARCIS KERETA API DENGAN MEMANFAATKAN MINIMUM SISTEM 8088 YANG DIHUBUNGKAN IBM PC-XT

# TUGAS AKHIR

Diajukan Guna Memenuhi Sebagian Persyaratan

Untuk Memperoleh Gelar

Sarjana Teknik Elektro

Pada

Bidang Studi Teknik Elektronika

Jurusan Teknik Elektro

Fakultas Teknologi Industri

Institut Teknologi Sepuluh Nopember

Surabaya

Mengetahui/Menyetujui

Dosen Pembimbing

IR. MOCH. HEROE

SURABAYA Oktober, 1994

# **ABSTRAK**

Salah satu pelayanan yang diharapkan oleh masyarakat pengguna jasa kereta api adalah pelayanan penjualan karcis kereta api yang cepat dan tepat. Alat bantu penjualan karcis kereta api ini membantu mempermudah tenaga operator loket dalam melayani pembeli.

Alat bantu penjualan karcis kereta api dilengkapi dengan alat pencetak untuk mencetak tanggal, tujuan, harga, memilih nomor tempat duduk serta mencetaknya. Dengan bantuan sebuah komputer IBM PC-XT, alat bantu penjualan karcis kereta api ini, menjadi lebih mudah dalam mentransfer data tempat duduk ke alat-alat yang sama di stasiun yang lain.

# KATA PENGANTAR

Dengan mengucap puji syukur kepada Allah S.W.T. atas berkat rahmatNya penulis dapat menyelesaikan tugas akhir ini dengan judul:

# SIMULASI ALAT BANTU PENJUALAN KARCIS KERETA API DENGAN MEMANFAATKAN MINIMUM SISTEM 8088 YANG DIHUBUNGKAN IBM PC-XT

Tugas akhir ini memiliki beban 6 SKS (Satuan Kredit Semester) yang disusun guna memenuhi persyaratan untuk memperoleh gelar sarjana pada Jurusan Teknik Elektro Fakultas Teknologi Industri, Institut Teknologi Sepuluh Nopember Surabaya.

Penyelesaian tugas akhir ini berlandaskan pada teori yang diperoleh penulis selama kuliah, buku-buku literatur, studi lapangan, bimbingan dosen dan pihak lain yang telah memberikan bantuan.

Walaupun demikian penulis menyadari sepenuhnya bahwa tugas akhir ini masih jauh dari sempurna dan tidak luput dari kekurangan. Oleh karenanya diharapkan adanya saran dan kritik dari pembaca demi kesempurnaannya.

Dalam kesempatan ini, penulis menyampaikan penghargaan dan ucapan terima kasih yang sebesar-besarnya kepada:

- Bapak Ir. Moch. Heroe, selaku dosen pebimbing yang banyak memberikan bimbingan dan dorongan dalam menyelesaikan tugas akhir ini

- Bapak Ir. Soetikno, selaku Koodinator Bidang Studi Elektronika.

- Bapak DR.IR. Moch.Salehhudin, M.Eng Sc selaku ketua jurusan Teknik Elektro FTI-ITS.

- Seluruh staf Seksi Niaga DAOP VIII PERUMKA.

- Istri dan anak yang telah memberikan banyak waktu hingga terselesainya tugas akhir ini.

- Semua pihak yang tidak dapat penulis sebutkan satu persatu, yang telah banyak memberikan dorongan dan pertimbangan hingga terselesainya tugas akhir ini.

Akhir kata semoga tugas akhir ini bermanfaat bagi para pembaca, khususnya untuk dikembangan lebih lanjut.

Surabaya, Oktober 1994

Penulis

# DAFTAR ISI

| BAB |                                        | HALAMAN |

|-----|----------------------------------------|---------|

|     | ABSTRAK                                | i       |

|     | KATA PENGANTAR                         | ii      |

|     | DAFTAR ISI                             | iv      |

|     | DAFTAR GAMBAR                          | viii    |

|     | DAFTAR TABEL                           | xi      |

| 1   | PENDAHULUAN                            | 1       |

|     | II.1 LATAR BELAKANG                    | 1       |

|     | II.2 PERMASALAHAN                      | 2       |

|     | II.3 PEMBATASAN MASALAH                | 3       |

|     | II.4 METODOLOGI                        | 4       |

|     | II.5 SISTEMATIKA PEMBAHASAN            |         |

|     | II.6 RELEVANSI                         | 6       |

| II  | TEORI PENUNJANG                        | ••••    |

|     | II.1 SISTEM MIKROPROSESSOR             | 10      |

|     | II.1.2 ARSITEKTUR SISTEM BUS           |         |

|     | II.1.2 SISTEM DAN FUNGSI ADDRESS BUS . |         |

|     | II.1.3 SISTEM DAN FUNGSI DATA BUS      |         |

|     | II.1.4 SISTEM DAN FUNGSI CONTROL BUS   |         |

|     | TT 4 5 ADDDDGG DDGG                    | 14      |

| II.2 CENTRAL PROCESSING UNIT 8088      |             |

|----------------------------------------|-------------|

| II.2.1 ARSITEKTUR CPU 8088             |             |

| II.2.2 REGISTER CPU 8088               | 23          |

| II.3 METODA PENGALAMATAN               | 30          |

| II.3.1 GATING                          | 30          |

| II.3.2 DECODING                        |             |

| II.4 BUFFER                            | 32          |

| II.5 MEMORY                            | 34          |

| II.5.1 READ ONLY MEMORY (ROM)          | 35          |

| II.5.1.1 KARAKTERISTIK ROM             | 35          |

| II.5.1.2 MEMBACA DATA ROM              | 37          |

| II.5.2 RANDOM ACCESS MEMORY (RAM)      | 38          |

| II.5.2.1 STATIC RANDOM ACCESS MEMORY ( | RAM)39      |

| II.5.2.2 DYNAMIC RANDOM ACCESS MEMORY  | (RAM)39     |

| II.5.2.3 MEMBACA DATA RAM              | 40          |

| II.5.2.4 MENULIS DATA RAM              | 42          |

| II.6 UNIT INPUT OUTPUT                 | 43          |

| II.6.1 PROGRAMABLE PERIPHERAL INTERFAC | E 825543    |

| II.6.2 FUNGSI PIN PPI 8255             | 46          |

| II.7 SISTEM KOMUNIKASI DATA            | 51          |

| II.7.1 TRANSFER DATA PARALEL           | 51          |

| II.7.2 TRANSFER DATA SERIAL            |             |

| II.7.3 METODA DAN STANDAR TRANSMISI    |             |

| SERIAI ACVNVDON                        | <b>5.</b> 4 |

|     | II.7.3.1 CURRENT LOOP 20 mA54                        |

|-----|------------------------------------------------------|

|     | II.7.3.2 RS-232C59                                   |

|     | II.7.3.3 KONFIGURASI HUBUNGAN RS-232C58              |

| ııı | PERENCANAAN SISTEM6                                  |

|     | III.1 PERENCANAAN PERANGKAT KERAS61                  |

|     | III.1.1 CLOCK63                                      |

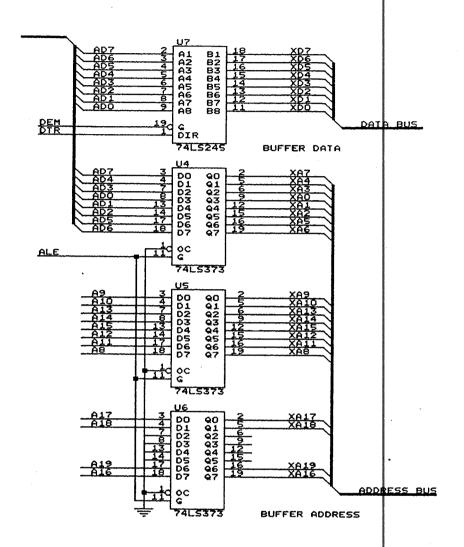

|     | III.1.2 BUFFER                                       |

|     | III.1 2 1 BUFFER DATA BUS65                          |

|     | III.1.2.2 BUFFER ADDRESS BUS65                       |

|     | III.1.2.3 BUFFER CONTROL BUS                         |

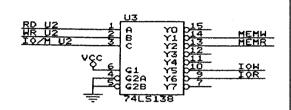

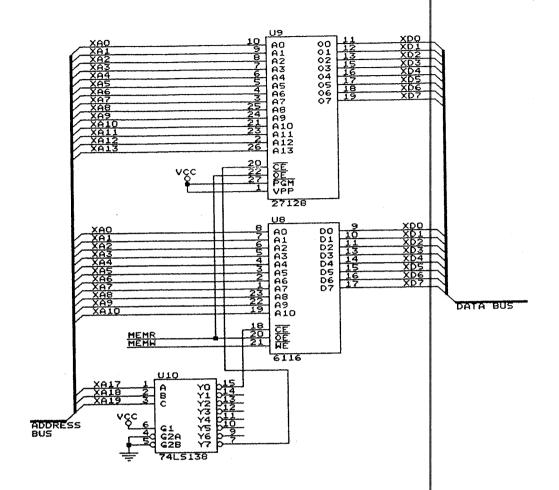

|     | III.1.3 RANGKAIAN DECODER MEMORY DAN MEMORY69        |

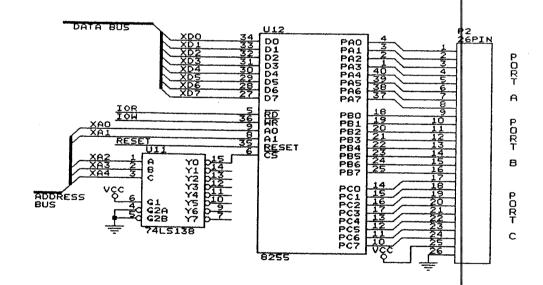

|     | III.1.4 RANGKAIAN DECODER UNIT INPUT OUTPUT73        |

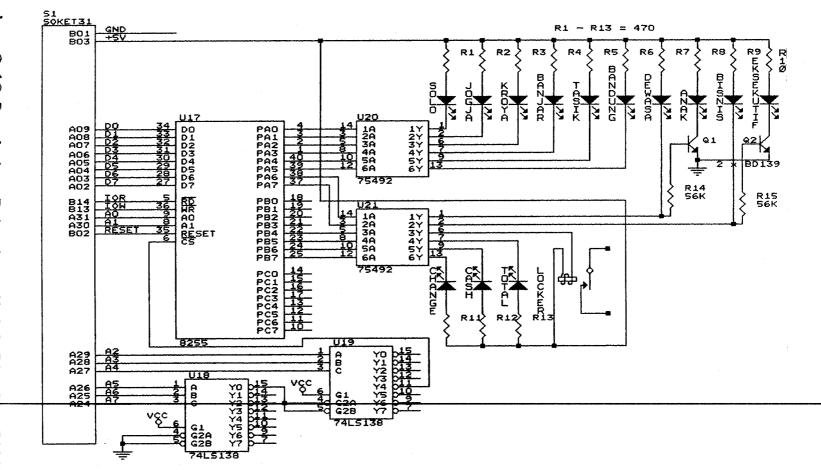

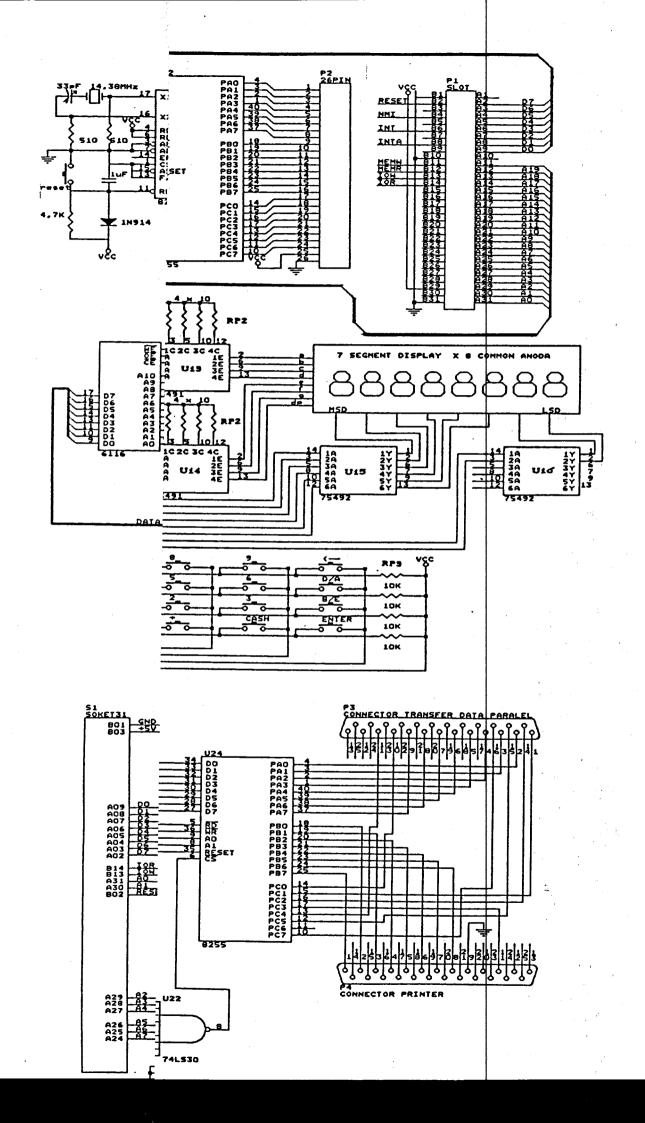

|     | III.1.5 RANGKAIAN CASH REGISTER (MESIN KAS)76        |

|     | III.1.5.1 RANGKAIAN DISPLAY 8 DIGIT                  |

|     | III.1.5.2 RANGKAIAN KEYBOARD MATRIK 4 k 479          |

|     | III.1.5.3 RANGKAIAN DISPLAY PILIHAN80                |

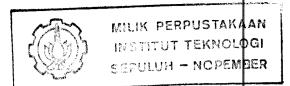

|     | III.1.6 RANGKAIAN INTERFACE TRANSFER DATA PARALEL 82 |

|     | III.1.6.1 INTERFACE TRANSFER DATA PARALEL            |

|     | PADA SISTEM MINIMUM 808883                           |

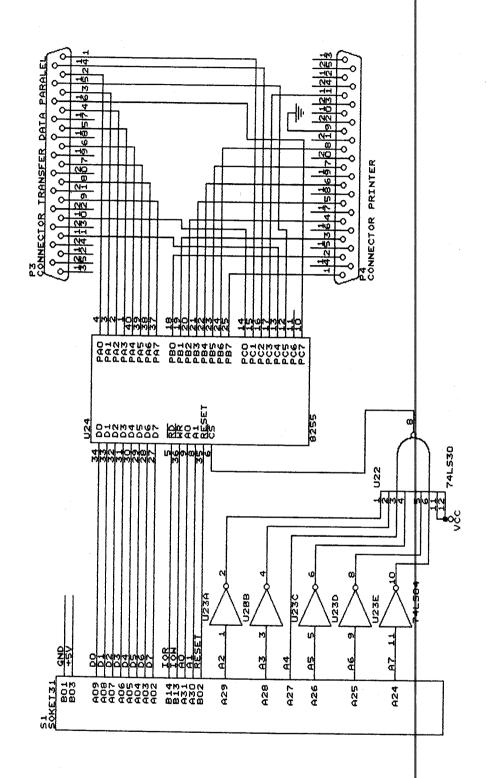

|     | III.1.6.2 INTERFACE TRANSFER DATA PARALEL            |

|     | PADA KOMPUTER IBM PC-XT85                            |

|     | III.1.7 RANGKAIAN INTERFACE TRANSFER DATA SERIAL .87 |

|     | III.2 PERENCANAAN PERANGKAT LUNAK                    |

|     | III.2.1 PERENCANAAN PERANGKAT LUNAK                  |

|    | PADA SISTEM MINIMUM 808891               |

|----|------------------------------------------|

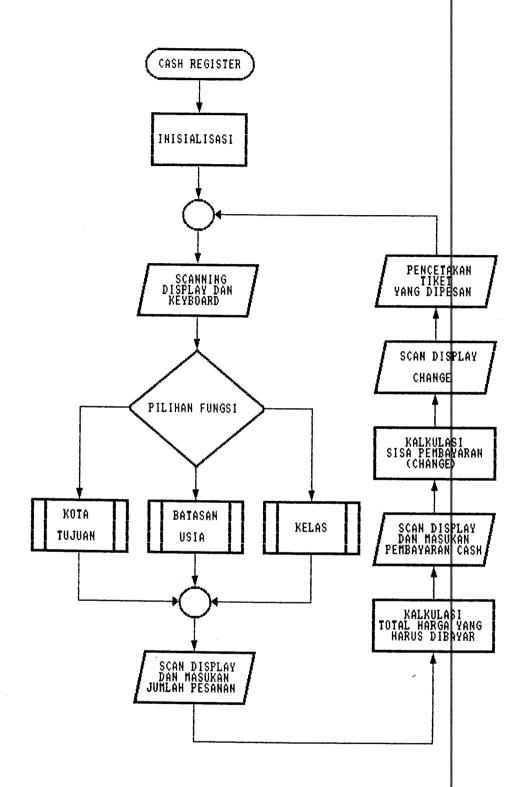

|    | III.2.1.1 PERENCANAAN PADA CASH REGISTER |

|    | (MESIN KAS)93                            |

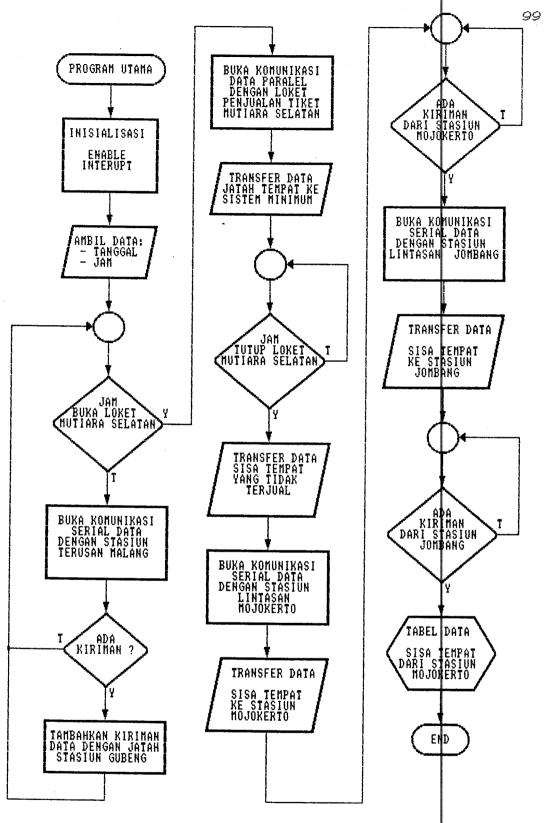

|    | III.2.2 PERENCANAAN PERANGKAT LUNAK      |

|    | PADA KOMPUTER IBM PC-XT98                |

| IV | PRINSIP KERJA DAN PENGOPERASIAN ALAT101  |

|    | IV.1 PRINSIP KERJA ALAT                  |

|    | IV.2 PENGOPERASIAN ALAT                  |

| ٧  | PENUTUP                                  |

|    | V.1 KESIMPULAN113                        |

|    | V.2 SARAN114                             |

|    | DAFTAR PUSTAKA                           |

|    | LAMPIRAN116                              |

# DAFTAR GAMBAR

| GAMBAR                            | HALAMAN |

|-----------------------------------|---------|

| 2.1 Sistem Microprosessor         |         |

| 2.2 Sistem Arsitektur Tiga Bus    |         |

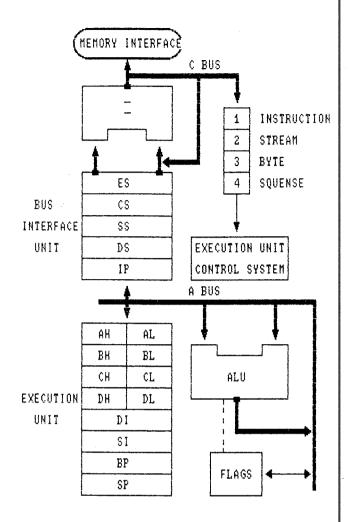

| 2.3 Organisasi Internal CPU 8088  |         |

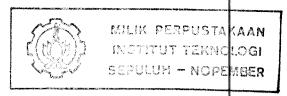

| 2.4 Bus Cycle CPU 8088            |         |

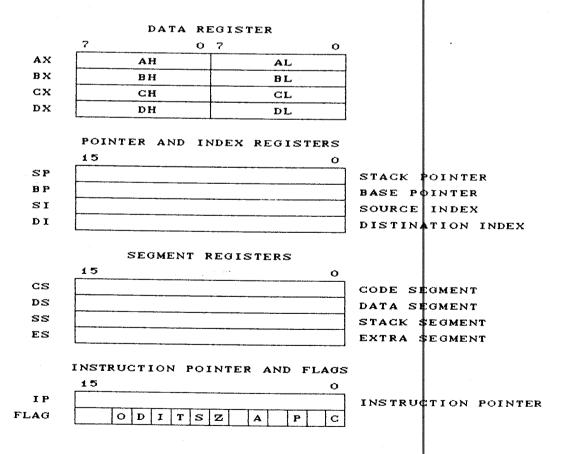

| 2.5 Register CPU 8088             | 24      |

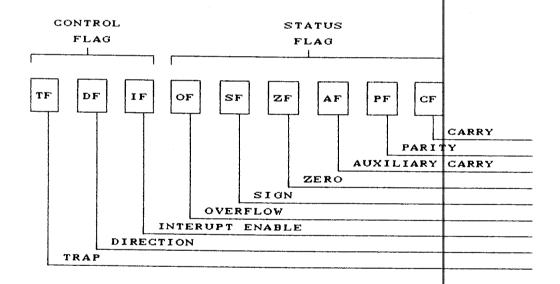

| 2.6 Flag Register CPU 8088        | 28      |

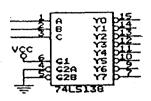

| 2.7 IC Decoder 74LS138            |         |

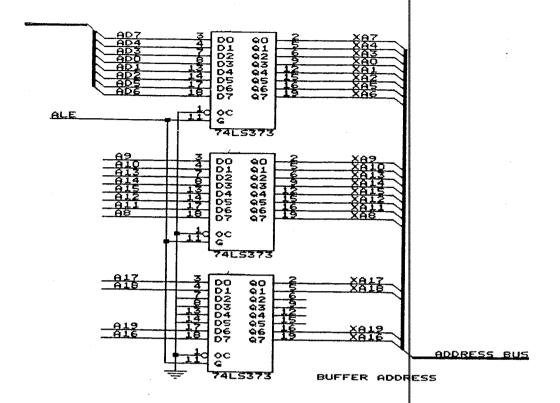

| 2.8 Buffer Address Bus            |         |

| 2.9 Buffer Data Bus               |         |

| 2.10 Block Diagram ROM            |         |

| 2.11 Diagram Waktu Baca Data ROM  |         |

| 2.12 Block Diagram RAM            | 40      |

| 2.13 Diagram Waktu Baca Data RAM  | 41      |

| 2.14 Diagram Waktu Tulis Data RAM | 42      |

| 2.15 Diagram Block PPI 8255       | 45      |

| 2.16 Register Control Wortd       | 47      |

| 2.17 Konfigurasi Pin-pin PPI 8255 | 49      |

| 2.18 Format Bit Serial Asinkron   |         |

| 2.19 Format Bit Serial Sinkron    | 53      |

| 2.20 Hubungan RS-232C Nult Modem                   | 60        |

|----------------------------------------------------|-----------|

| 2.21 Hubungan RS-232C Tanpa Handshake              | 60        |

| 3.1 Block Diagram Rencana Sistem                   | 62        |

| 3.2 Konfigurasi IC 8284                            | 63        |

| 3.3 Rangkaian Clock 4,77 MHz DC 33 %               | 64        |

| 3.4 Rangkaian Buffer Address dan Data Bus          | 66        |

| 3.5 Rangkaian Buffer Control Bus                   | 69        |

| 3.6 Mapping Memory                                 | 70        |

| 3.7 Rangkaian Decoder Memory dan Memory            | 72        |

| 3.8 Mapping I/O                                    |           |

| 3.9 Rangkaian Decoder Unit I/O                     |           |

| 3.10 Buffer Display 8 Digit dan Keyboard 4         | x 478     |

| 3.11 Mapping I/O Interface Modul Display P         | llihan80  |

| 3.12 Rangkaian Interface Modul Display Pil         | ihan81    |

| 3.13 Mapping I/O Interface Transfer Data Page 1.13 | aralel    |

| pada Sistem Minimum 8088                           | 83        |

| 3.14 Rangkaian Interface Modul Transfer Da         | a Paralel |

| pada Sistem Minimum 8088                           | 84        |

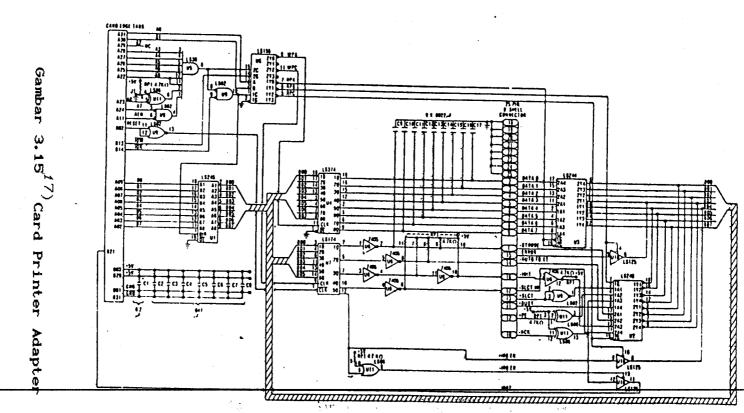

| 3.15 Card Printer Adapter                          | 86        |

| 3.16 Rangkaian Pengendali Arah pada Card P         | inter87   |

| 3.17 Rencana Sistem Komunikasi Data Antar (        | tasiun88  |

| 3.18 Card Serial Adapter                           |           |

| 3.19 Rangkaian Pengembangan COM1                   | 90        |

| 3 20 Diagram Alin Ponondhot Lunch                  |           |

|      | pada Sistem Minimum 808892                          |

|------|-----------------------------------------------------|

| 3.21 | Diagram Alir Perangkat Lunak pada Cash Register .95 |

| 3.22 | Diagram Alir Perangkat Lunak                        |

|      | pada Komputer IBM PC-XT99                           |

| 4.1  | Blok Diagram Prinsip Kerja Alat103                  |

| 4.2  | Pengawatan Komunikasi Serial dan Paralel106         |

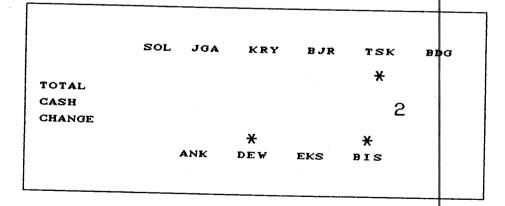

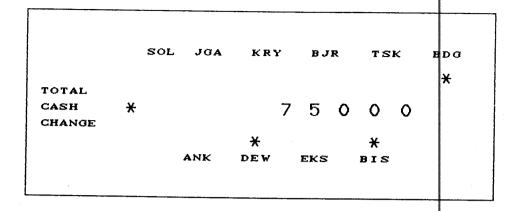

| 4.3  | Tampilan Display Alat Cash Register107              |

# DAFTAR TABEL

|                                          | İ            |

|------------------------------------------|--------------|

| TABEL                                    | HALAMAN      |

| 2.1 Jatah Tempat Duduk Mutiara Selatan   | 8            |

| 2.2 Jam Perjalanan dan Harga Karcis Muti | ara Selatan9 |

| 2.3 Segment Register Saat Cycle Bus      | 19           |

| 2.4 Operasi Bus Cycle Mode Minimum       | 23           |

| 2.5 Operasi Register CPU 8088            | 26           |

| 2.6 Penggunaan Segmen Register dan Offse | 28           |

| 2.7 Read Write Register                  | 50           |

| 3.1 Tabel Kebenaran Control Bus          | 68           |

| 3.2 Perencanaan Decoder Unit Memory      | 71           |

| 3.3 Perencanaan Decoder Unit I/O PPI 825 | 5            |

# BAB I PENDAHULUAN

#### I.1 LATAR BELAKANG

Perkembangan teknologi yang semakin maju saat ini, dimaksudkan untuk mencapai efisiensi dan efektifitas yang lebih tinggi. Salah satunya adalah pemakaian Sistem Minimum untuk mengontrol kerja suatu alat. Hal ini dimungkinkan untuk mesinkronkan alat-alat tersebut dengan komputer, sehingga didapat suatu pengendalian alat-alat dengan komputer. Penggunaan komputer dewasa ini telah meluas keberbagai bidang profesi dan industri baik perangkat lunak, maupun perangkat kerasnya, seperti dalam bidang Telekomunikasi, Meterologi, Pengolahan Data serta dalam Jasa pelayanan.

Dalam bidang jasa pelayanan, pemakaian komputer untuk mendistribusikan tempat duduk dari stasiun terusan ke stasiun lintasan, atau dari stasiun lintasan kestasiun lintasan tujuan berikutnya. Sehingga dimungkinkan untuk menstransfer jumlah dan nomor tempat duduk yang tidak terjual antar stasiun dengan cepat dan akurat, tentunya hal ini dapat 'lebih mengoptimalkan penjualan

karcis kereta api. Komputer sebagai instrumen dimanfaatkan sebagai pengendali komunikasi data tempat duduk ke loket-loket penjualan. Sedangkan pada masing-masing loket dilayani dengan sebuah mesin kas uang (cash register), sekaligus pemilih tempat duduk yang memanfaatkan sistem minimum.

Secara langsung teknologi komputer telah memberikan dampak yang sangat luas bagi kehidupan manusia kini

dan akan datang. Sesuai dengan tuntutan ketelitian dan

kecepatan setiap bidang pekerjaan yang kini semakin

meningkat, sehingga pemikiran kearah penggunaan komputer

sebagai salah satu alternatif merupakan suatu keputusan

yang terbaik.

#### I.2. PERMASALAHAN

Saat ini pada beberapa stasiun, sistem komunikasi data tempat duduk masih memakai telegram dan telephone untuk menyampaikan jumlah dan nomor tempat duduk yang tidak terjual dari stasiun ke stasiun berikutnya. Sistem ini banyak sekali kelemahannya, utamanya kecepatan dan keakuratan.

Sistem penjualan karcis di loket-loket yang masih menggunakan tenaga operator penuh dalam melayani penjualan karcis akan terasa lambat pada hari-hari tertentu.

#### I.3. PEMBATASAN MASALAH

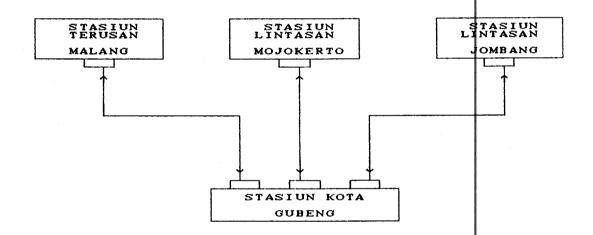

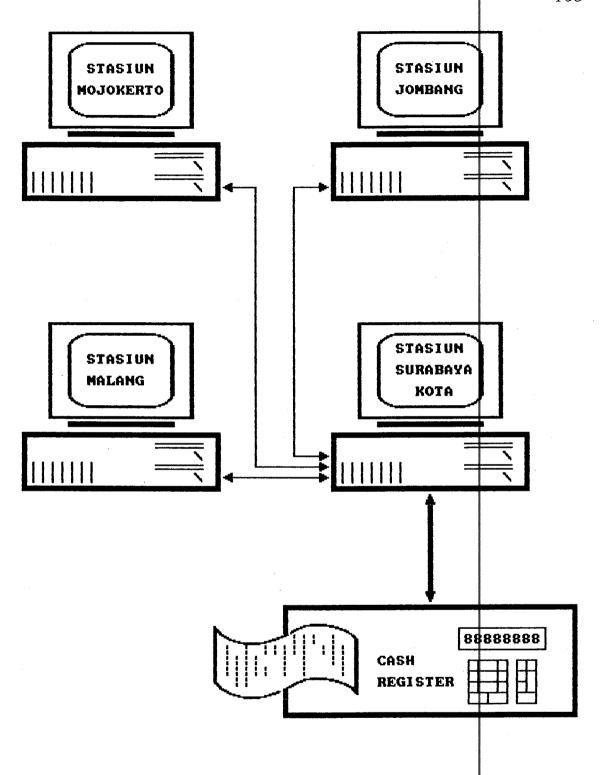

Untuk membatasi permasalahan, maka dalam tugas akhir ini direncanakan otomatisasi pada| tiga stasiun lintasan dan satu stasiun terusan. Sedangkan loket jurusan yang dipilih untuk transportasi kereta api Mutiara Selatan Surabaya ke Bandung di stasiun Surabaya Gubeng. Stasiun terusan Malang, stasiun lintasan Mojokerto dan stasiun lintasan jombang dengan pengendali stasiun Surabaya-Gubeng dipilih untuk aktifitas komunikasi data tempat duduk.

Dalam tugas akhir ini direncanakan pembuatan sebuah alat bantu penjualan karcis yang ditempatkan diloket untuk jurusan Surabaya - Bandung (Mutiara Selatan) dengan memanfaatkan sistem minimum 8088 dihubungkan dengan IBM PC-XT. Sistem minimum 8088 mengendalikan sebuah mesin kas uang (cash register) dan alat pencetak untuk memilih dan mencetak nomor tempat duduk yang dipesan.

Sistem minimum 8088 dihubungkan IBM PC-XT dengan komunikasi data paralel dimaksudkan IBM PC-XT sebagai pusat data yang mengatur penjatahan tempat duduk ke masing-masing loket dari sebuah stasiur. Pemanfaatan adapter printer yang seharusnya digunakan untuk printer, dengan sedikit modifikasi bisa digunakan untuk komuni-

kasi data paralel yang biasa digunakan untuk komunikasi jarak dekat.

Untuk mendistribusikan data tempat duduk, atau untuk menstransfer jumlah dan tempat duduk yang tidak terjual dari stasiun terusan ke stasiun lintasan, atau dari digunakan komunikasi data serial yang biasa digunakan komunikasi jarak jauh, yang fasilitasnya disediakan komputer IBM PC-XT.

#### I.4. METODOLOGI

Perencanaan alat ini berdasarkan pertimbangan dari permasalahan yang ada.

Pertama: mesin kas uang (cash register), merupakan alat bantu petugas loket untuk mengkalkulasi uang dan penjatahan tempat duduk pesanan penumpang.

Kedua: Komputer pusat stasiun untuk menstranfer data tempat duduk ke loket, dan mentransfer tempat duduk yang tidak terjual ke stasiun berikutnya.

Untuk memperoleh penyelesaian dari masalah diatas, maka metode yang dipakai sebagai berikut:

Pertama: Peninjauhan dilapangan tentang cara kerja penjualan karcis kereta api, dan mekarisme tempat duduk yang tidak terjual.

Kedua : Mencari alternatif yang terbaik untuk memper-

oleh penyelesaian yang sesuai.

Ketiga: Dari pemilihan alternatif dari sistem umum yang dipakai oleh PERUMKA, maka dapat menentukan metode yang dipakai untuk penyelesaiannya yang berupa pembuatan sistem minimum 8088 yang dihubungkan dengan IBM PC-XT.

# I.5. SISTEMATIKA PEMBAHASAN

Pada tugas akhir ini pembahasan dilakukan dengan pembagian menjadi lima bab sebagai berikut:

- Bab I : Dibahas tentang pendahuluan yang menjadi latar belakang, permasalahan, batasan masalah, metodologi dan sistematika pembahasan

- Bab II: Dijelaskan mengenai teori pendukung sistem minimum 8088, interface komunikasi data paralel dan serial dari IBM PC-XT.

- Bab III: Dibahas mengenai perencanaan rangkaian dan komponen yang digunakan serta pembuatan perangkat

lunak untuk mengontrol sistem keseluruhan.

- Bab IV: Dibahas mengenai prinsip kerja dan pengoperasian alat.

- Bab V : Merupakan penutup yang berisi kesimpulan dari seluruh pengamatan dan percobaan selama mengerjakan tugas akhir.

## I.6. RELEVANSI

Dengan selesainya tugas akhir ini diharapkan peralatan yang telah dibuat bermanfaat langsung bagi masyarakat pemakai jasa PERUMKA. Bagi PERUMKA sendiri diharapkan bisa lebih efisien dan efektif dalam pengaturan dan penjatahan tempat duduk. Selanjutnya dengan semakin efektifnya dalam pengaturan dan penjatahan tempat duduk tersebut, pada akkhirnya PERUMKA diharapkan bisa mengoptimalkan penjualan karcis kereta api.

# BAB II TEORI PENUNJANG

Salah satu Badan Usaha Milik Negara (BUMN) yang melayani transportasi darat adalah PERUMKA. Sebagai BUMN, PERUMKA harus beroreantasi untuk kepentingan masyarakat, dan sebagai perusahaan pada umumnya harus tetap mencari keuntungan. Perusahaan Umum Kereta Api dengan Seksi Niaga sebagai ujung tombak pelayanan penumpang atau barang berupaya memperbaiki mutu pelayanan pada masyarakat pengguna jasa kereta api.

Salah satu pelayanan yang diberikan PERUMKA adalah pelayanan karcis dengan kemudahan pembelian karcis terusan. Sebagai contoh untuk Stasiun Malang melayani penjualan karcis untuk jurusan|ke Bandung (kereta api Mutiara Selatan) dengan Stashun transit Surabaya-Kota (Gubeng). Demikian juga untuk calon penumpang yang akan bepergian ke Bandung dari dapat membeli karcis di Jember, dan transit | di Stasiun Gubeng. Tabel 2.1 memperlihatkan penjatahan | kursi pada stasiun-stasiun terusan dan lintasan kereta api Mutiara Selatan (41) dengan dua kelas, Eksekutif K1/1 dan K1/2 dan Bisnis K2/1 ; K2/2 ; K2/3 ; K2/4 dan K2/5.

Tabel 2.1 Jatah Tempat Duduk Mutiara Selatan

|            | JA'             | TAH TEMP        | AT DUDUK        | MUTIARA         | SELATAN         | (41)            |                 |        |

|------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|--------|

| STASIUN    | K1/1            | K1/2            | K2/1            | K2/2            | K2/3            | K2/4            | K2/5            | JUMLAH |

| SB.KOTA    | 01A-04B<br>(14) | 01A-03D<br>(12) | 15C-17D<br>(08) | 12C-17D<br>(20) | -               | 01A-17D<br>(64) | 12C-17D<br>(20) | 138    |

| SB.GUBENG  | 04C-12D<br>(34) | 04A-10D<br>(28) | -               | @1A-12B<br>(44) | 01A-17D<br>(64) | ~               | 06C-12B<br>(24) | 194    |

| MOJOKERTO  | -               | -               | 05A-06B<br>(06) |                 |                 | -               | _               | 6      |

| JOMBANG    | -               | -               | 06C-08B<br>(08) | _               | -               | -               | -               | 8      |

| KERTOSONO  | -               | -               | 08C-10D<br>(10) | -               | -               | -               | -               | 10     |

| NGANJUK    | -               | -               | 12A-12D<br>(94) | -               | -               | -               | -               | 4      |

| MADIUN     | 13A-13D<br>(04) | -               | -               | -               | <u>-</u>        | _               | 01A-06B<br>(20) | 24     |

| solo       |                 | 11A-13D<br>(12) | -               | -               | -               | -               | ~               | 12     |

| MALANG     | -               | -               | 01A-02D<br>(06) | -               | -               | -               | -               | 6      |

| BLITAR     | _               | -               | 11A-11B<br>(Ø2) | -               | -               |                 | -               | 2      |

| KEDIRI     | -               | -               | 11C-11D<br>(02) | <u>.</u>        | -               | -               | -               | 2      |

| JEMBER     | -               | -               | 13A-15B<br>(10) | -               | -               | -               | -               | 10     |

| Banyuwangi | -               | •••             | 03A-04B<br>(08) | -               | -               | <b>-</b> .      | -               | 8      |

Penjatahan penjualan karcis mempunyai kerugian apabila dari stasiun-stasiun terusan tidak terjual, harus segera diberitakan ke stasiun transit Stasiun Gubeng untuk dijual di Stasiun Gubeng, atau stasiun-stasiun lintasan kereta yang lain. Dan

pengaturan kapan saatnya data tempat duduk bisa ditransfer ke stasiun berikutnya bergantung pada jam berangkat kereta bersangkutan. Tabel 2.2 berikut adalah jam berangkat dan datang, serta harga karcis kereta Mutiara Selatan pada stasiun lintasan.

Tabel 2.2. Jam Perjalanan dan Harga Karcis Kereta Mutiara Selatan

| STASIUN         DATANG         PERGI         EKS. A         BIS. DW         BIS.           SB.Kota         -         17:30                                                                                                                                                                                                                                                                                                           | AN |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| SB.Gubeng       17:37       17:45         Wonokromo       -       -         Mojokerto       18:12       18:15         Jombang       18:42       18:45         Kertosono       19:11       19:16         Nganjuk       19:38       19:41         Madiun       20:23       20:28         Solo       21:56       21:58       36000       21000       1600         Jogjakarta       23:02       23:25       36000       21000       1600 |    |

| Wonokromo       -       -         Mojokerto       18:12       18:15         Jombang       18:42       18:45         Kertosono       19:11       19:16         Nganjuk       19:38       19:41         Madiun       20:23       20:28         Solo       21:56       21:58       36000       21000       1600         Jogjakarta       23:02       23:25       36000       21000       1600                                           |    |

| Mojokerto       18:12       18:15         Jombang       18:42       18:45         Kertosono       19:11       19:16         Nganjuk       19:38       19:41         Madiun       20:23       20:28         Solo       21:56       21:58       36000       21000       1600         Jogjakarta       23:02       23:25       36000       21000       1600                                                                             |    |

| Jombang       18:42       18:45         Kertosono       19:11       19:16         Nganjuk       19:38       19:41         Madiun       20:23       20:28         Solo       21:56       21:58       36000       21000       1600         Jogjakarta       23:02       23:25       36000       21000       1600                                                                                                                       |    |

| Kertosono       19:11       19:16         Nganjuk       19:38       19:41         Madiun       20:23       20:28         Solo       21:56       21:58       36000       21000       1600         Jogjakarta       23:02       23:25       36000       21000       1600                                                                                                                                                               |    |

| Nganjuk       19:38       19:41         Madiun       20:23       20:28         Solo       21:56       21:58       36000       21000       1600         Jogjakarta       23:02       23:25       36000       21000       1600                                                                                                                                                                                                         |    |

| Madiun       20:23       20:28                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Solo     21:56     21:58     36000     21000     1600       Jogjakarta     23:02     23:25     36000     21000     1600                                                                                                                                                                                                                                                                                                              |    |

| Jogjakarta 23:02 23:25 36000 21000 1600                                                                                                                                                                                                                                                                                                                                                                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0  |

| Kroya 01:31 01:37 36000 21000 1600                                                                                                                                                                                                                                                                                                                                                                                                   | 00 |

| Banjar 03:10 03:22 40000 21000 1600                                                                                                                                                                                                                                                                                                                                                                                                  | 10 |

| TasikMalaya 04:10 04:17 40000 21000 1600                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

| Bandung 06:58 - 44000 23000 1800                                                                                                                                                                                                                                                                                                                                                                                                     | 00 |

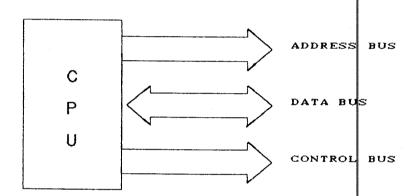

# II.1. SISTEM MIKROPROSESSOR

Sistem mikroprosessor merupakan kumpulan dari beberapa unit sistem yang menjadi satu kesatuan, yaitu :

- CPU (Central Processing unit)

- Unit Memori

- Unit Input/Output.

Sistem mikroprosesor yang standar yang merupakan kumpulan dari unit CPU, unit Memory dan Unit Input/Output seperti pada gambar 2.1, mempunyai hubungan antara unit-unit yang direalisasikan dalam arsitektur sistem tiga bus yaitu:

- Address bus

- Data bus

- Kontrol bus.

Gambar 2.1 Sistem Mikroprossesor

#### II.1.1. ARSITEKTUR SISTEM BUS

Sistem bus dalam CPU adalah sekumpulan sinyal data bit yang saling terkait satu bit dengan bit yang lain, atau antara satu bus dengan bus yang lain untuk mensinkrokan CPU. Dikelompokkan berdasarkan fungsinya. Pada CPU dibedakan dalam dua bus, yaitu Internal Bus dan External Bus. Sinyal-sinyal yang terdapat pada CPU 8 bit dapat digolongkan menjadi tiga buah sistem bus

Gambar 2.2 Sistem Arsitektur Bus

(Tiga Bus Arsitektur), yakni:<sup>2)</sup>

1. Sistem Address Bus.

Rodnay Zaks, Mikroprocessor from chip to system (Sybex, Inx., 1980), p. 41

<sup>2)</sup> James W. Coffrom, Practical Hardware Details For 8080,8085, Z80, and 6800 Mikroprocessor System. New Jersey: Prentice-Hall, Inc., 1981, p. 3

- 2. Sistem Data Bus.

- 3. Sistem Kontrol Bus.

Blok diagram CPU dengan tiga bus arsitektur dapat dilihat pada gambar 2.2.

# II.1.2. SISTEM DAN FUNGSI ADDRESS BUS

CPU 8 bit sistem address busnya merupakan output yang dapat berhubungan dengan bus lain. Karena address bus merupakan output maka hanya mempunyai satu arah saja (Unidirectional). Jumlah address bus menentukan besar kecilnya kemampuan CPU tersebut untuk berhubungan dengan memory. Misalnya CPU 8088 yang mempunyai 20 address bus (AO-A19), maka CPU tersebut mampu memberi alamat pada memori sebesar 2<sup>20</sup> = 1024 Kbyte lokasi.

Pada CPU 8088 yang biasa disebut sebagai CPU 8 bit, delapan bit address orde rendahnya digunakan untuk menentukan port I/O. Jadi I/O yang dapat dihubungi sebanyak 256 port dari OOH sampai FFH. Address bus merupakan keluaran dari cpu, fungsi dari address bus adalah untuk menentukan alamat atau memilih suatu lokasi memori atau port I/O untuk berkomunikasi dengan CPU. Dalam address bus CPU 8088 busnya juga menjadi bagian dari pada data bus dan control bus. Untuk itu CPU 8088 ini harus dipisahkan bus yang dipakai bersama.

# II.1.3. SISTEM DAN FUNGSI DATA BUS

CPU bit sistem data busnya merupakan input/output data dari/ke CPU (bidirect|onal). Pada waktu write, data ditransfer dari CPU ke | memori atau peripheral, sedang waktu read data ditransfer dari memori atau peripheral ke CPU. Meskipun data bus mempunyai sifat bidirectional, tetapi dalam waktu yang bersamaan tidak dapat digunakan untuk mengirim menerima data. Fungsi dari data bus yaitu| menyediakan jalur untuk pertukaran informasi data antara CPU dengan komponen pendukung sistem minimum yang telah dipilih oleh address bus.

# II.1.4. SISTEM DAN FUNGSI CONTROL BUS

CPU 8 bit sistem kontrol busnya merupakan output yang mempunyai empat buah sinyal yang tersabung dalam kontrol bus dengan fungsi sama sebagai kontrol pada CPU. Keempat sinyal tersebut yaitu:

- 1. Memory Read (MEMR)

- 2. Memmory Write (MEMW)

- 3. I/O Read (IOR)

- 4. I/O Write (IOW)

Seperti halnya address bus, maka kontrol bus

merupakan sinyal yang bersifat satu arah (unidirectio-nal). Bila CPU sedang membaca data dari/ke memory maka sinyal MEMR/MEMW aktif, dan bila CPU sedang membaca data data/ke I/O maka sinyal IOR/IOW akan diaktifkan. Fungsi dari kontrol bus adalah menentukan hubungan kerja CPU dengan memory atau I/O, baik untuk kondisi R/W.

# II.1.5. ADDRESS DECODING DAN BUFFFERING

Untuk berkomunikasi dengan memory ROM atau RAM, atau peralatan I/O, maka diperlukan suatu cara agar CPU dapat memilih atau menentukan salah satu IC atau peralatan tertentu saja yang dapat diajak berkomunikasi dengan mengaktifkan CS-nya (Chip Select). Hal ini dapat dilaksanakan dengan Address decoding. Sinyal-sinyal pada address bus di decode sedemikian rupa sehingga setiap kombinasi pada address akan menghasilkan satu sinyal pilih yang akan mengaktifkan salah satu IC atau peralatan yang sedang dikerjakan oleh CPU.

Kemampuan dibebani (Fan Out) CPU terbatas, sedangkan CPU harus mendrive komponen penunjang lainnya dengan jarak antara CPU dengan peralatan cukup jauh, untuk itu dibutuhkan suatu komponen buffer untuk menguatkan arus yang keluar dari CPU, sehingga bila CPU akan dihubungkan dengan peralatan lain yang cukup jauh,

maka arus yang disuplay dari CPU masih berada dalam batas-batas yang diijinkan.

# II.2. CENTRAL PROCESSING UNIT 8088

CPU 8088 produksi intel, dan merupakan hasil pengembangan dari mikroprosesor 8086. Pada CPU 8088 terdapat delapan bit jalur data yang terhubung, tetapi jumlah jalur bit data internalnya adalah 16 bit. Tipe CPU seperti CPU 8088 dapat digolongkan sebagai CPU 16 bit.

Keterangan untuk Arsitektur internal dan fungsi untuk masing-masing pin, baik input maupun output dapat dijelaskan sebagai berikut:

# II.2.1. ARSITEKTUR CPU 8088

CPU 8088 sebagai pusat pengendali dari sistem minimum, dan merupakan CPU 16 bit yang memiliki 8 bit data bus. Walaupun demikian instruksinya dapat memanipulasi data 16 bit, tetapi data dan instruksinya diambil dan ditulis ke memory 8 bit satu persatu pada siklus tertentu. CPU ini mampu mengakses sampai satu Megabyte yang dapat berupa data atau program.

CPU 8086 mempunyai 16 bit interrnal maupun eksternal data bus, sedangkan pada CPU 8088 mempunyai in-

Gambar 2.3. 3) Organisasi Internal CPU 8088.

ternal data 16 bit dan eksternal data bushya 8 bit, sedangkan perangkat lunak untuk keduanya sama.

Salah satu keunikan dari CPU 8088 dibandingkan dengan tipe CPU sekelasnya adalah kemampuannya untuk mengakses memory lebih dari 65.536 bytes yang mampu diakses oleh 16 bit address field. CPU 8088 mempunyai

Intel, Microsystem Components Handbook-Mikroprocessor Volume 1 (Intel Co, 1985) hal 3-106

kemampuan peng-address-an 20 bit yang memungkinkan peng-aksesan 1.0448.576 lokasi memory. Tetapi karena instruksi-instruksinya hanya mengizinkan operasi dan manipulasi address 16 bit, maka seakan-akan hanya 65.536 bytes saja yang dapat diakses.

Pada gambar 2.3 dapat dilihat diagram blok dari rangkaian internal CPU 8088 dan juga pin-pinnya. CPU 8088 dapat dioperasikan dalam dua mode yang ditentukan oleh kondisi pin MN/MX. Apabila pin MN/MX berlogika tinggi maka mode oprasinya adalah minimum, pada kondisi ini CPU 8088 dapat dioperasikan sama seperti CPU 8085. Dan apabila pin MN/MX diberi logika rendah, maka CPU 8088 dioperasikan dalam mode maximum.

CPU 8088 mempunyai beberapa buah pin yang dapat digunakan baik pada mode minimum maupun mode maximum. Pada gamabar 2.3 ditunjukan perbedaan fungsi pin 24 sampai dengan pin 31 dan pin 34 jika CPU 8088 dioperasikan dalam mode maximum. Berikut adalah penjelasan pin-pin pada CPU 8088 baik dalam mode minimum maupun mode maximum:

# - ADO - ADF7 (Address Data Bus)

Merupakan jalur addres dan data yang bekerja secara multiplex. Jalur ini akan bekerja sebagai address (AO sampai A7) pada bus cycle yang pertama (T1) dan pada bus cycle berikutnya (T2,T3

dan T4) jalur ini akan berfungsi sebagai jalur data. Pada gambar 2.4 terlihat timming diagram dari bus cycle dari sistem. Disini dapat dilihat

Gambar 2.4.4) Bus Cycle CPU 8088.

untuk jalur ADDR/DATA dapat berfungsi baik sebagai address maupun data yang tergantung dari bus cycle.

- A8 - A15 (Address Bus)

<sup>4)</sup> Ibid, hal. 3-115

Merupakan address bus untuk seluruh bus cycle (T1 - T4).

# - A16/S3 - A19/S6 (Address/Status)

Jalur ini berfungsi sebagai jalur address status yang bekerja secara multiplex. Selama bus cycle yang pertama (Ti), jalur ini berfungsi bagai address (A16 - A19) untuk operasi memory. Pada bus cycle berikutnya jalur ini berfungsi sebagai penunjuk status dari CPU 8088. S6 dalam kondisi rendah. Pada setiap permulaan kondisi bus cycle, S5 akan menunjukan status dari interupt enable flag. S4 dan S3 merupakan penunjuk dari segment register yang digunakan untuk

Tabel 2.3. Segment Register saat Cycle Bus<sup>5)</sup>

| S4 | S3 | SEGMENT                |

|----|----|------------------------|

| 0  | 0  | Alternate Data Segment |

| 0  | 1  | Stack Segment          |

| 1  | 0  | Code Segment           |

| 1  | 1  | Data Segment           |

mengakses data, seperti ditunjukan tabel 2.3.

- RD (read)

Sinyal read menyatakan bahwa CPU 8088 | melaksana-

Ibid, hal 3-107

kan operasi membaca memory atau I/O, yang tergantung pada status yang terdapat pada pin IO/M.

Jika RD rendah dan IO/M tinggi maka yang dilakukan adalah operasi membaca I/O. Sedangkan jika RD rendah dan IO/M rendah maka yang dilakukan adalah operasi membaca memory.

#### READY

Adalah suatu sinyal pemberitahuan yang menyatakan bahwa transfer data pada peralatan I/O atau memory telah selesai.

# - INTR (Interupt Request)

Merupakan sinyal maskable interupt yang digunkan untuk meng-interupt CPU 8088. Sinyal tersebut aktif tinggi. Pada proses pelayanan interupt, harus ada routine interupt yang dilaksanakan dimana address awal routine ini ditunjukan oleh vektor interupt yang terdapat dalam memory.

#### - TEST

Merupakan sinyal input yang akan dipergunakan oleh intruksi ' wait for test'. Jika sinyal ini rendah, maka operasi dilanjutkan dan jika tinggi, maka CPU tidak akan melakukuan apa-apa.

- NMI (Non Maskable Interupt )

Merupakan jenis interupt yang berasal dari perangkat keras (Hard Ware) dan interupt ini tidak

bisa dihalangi oleh perangkat lunak (Soft Ware).

#### - RESET

Dengan adanya sinyal RESET ini, maka CPU 8088 akan menghentikan semua operasi yang sedang berlangsung, dan intruksi yang dijalankan mulai dari awal lagi.

### - CLK ( Clock )

CLK merupakan input clock dari CPU 8088 dan bus controller dan berfungsi untuk mengatur timing dari operasi CPU 8088 dan bus controller.

# - MN/MX ( Minimum/Maximum )

Suatu logika yang diberikan kepada pin ini menyatakan mode operasi dari CPU 8088. Jika input pin ini rendah maka CPU 8088 beroperasi dengan mode maksimum, sebaliknya jika input pin ini tinggi maka CPU 8088 beroperasi dengan mode minimum.

#### - VCC

Merupakan pin power supply. Besar tegangan input yang diberikan pada pin ini adalah + 5 Volt dengan toleransi 10%.

#### - GND ( Ground )

Merupakan pin ground dari CPU.

Berikut ini adalah penjelasan pin-pin 8088 bila

dioperasikan dalam mode minimum. 6)

# - TO/M ( Status Line)

Berfungsi untuk membedakan CPU 8088 mengakses memory atau I/O. Bila kondisinya rendah menyatakan I/O diakses dan bila kondisinya tinggi menyatakan memory yang diakses.

- INTA ( Interupt Acknowledge )

Menyatakan bahwa CPU 8088 telah mendeteksi adanya permintaan interupt.

- ALE ( Address Latch Enable )

Merupakan sinyal output dari CPU 8088 yang digunakan untuk menyimpan address ke dalam address latch.

- DT/R ( DATA TRANSMIT/RECEIVE )Diperlukan untuk mengatur arah pengiriman data pada bus transceiver.

## - HOLD, HLDA

Hold digunakan apabila sebuah CPU lain mempergunakan bus, dengan memerintahkan CPU 8088 untuk melepaskan sistem bus, sehingga sistem bus dapat dipakai oleh CPU yang lain.

- DEN ( Data Enable )

Sinyal ini berfungsi agar data transceiver dapat

<sup>6)</sup> Intel, loc cit

Tabel 2.4. Operasi Bus Cycle Mode  $Minimum^7$

| IO/M                            | DT/R                                 | SSO                             | OPERASI                                                                                             |

|---------------------------------|--------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------|

| 1<br>1<br>1<br>1<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0 | Interupt Acknowledge Read I/O port Write I/O port Halt Code Access Read Memory Write Memory Passive |

di-enable. DEN ini aktif rendah untuk masingmasing I/O dan mengakses memory pada INTA cycles.

# - SSO ( Status Line )

Merupakan status line yang bersama-sama dengan 10/M dan DT/R membentuk suatu sistem decoding dari status bus cycle. Pada tabel 2.4. dapat dilihat fungsi yang dibentuk oleh ketiga sinyal tersebut.

# II.2.2. REGISTER CPU 8088

CPU 8088 mempunyai 14 buah register 16 bit.

Register-register ini dikelompokan beberapa group,

yaitu:

<sup>7)</sup> Intel, loc cit

- Data Register

- Pointer dan Index Register

- Segment register

- Instruction pointer register dan Flag register Pengelompokan dari register CPU 8088 dapat dilihat pada gambar 2.5.

Data group terdiri atas empat buah register yaitu: AX, BX, CX, dan DX. Register-register 16 bit ini dapat dioperasikan baik untuk operasi 8 bit. Jika register-register dioperasikan untuk operasi 8 bit, maka tiap

Gambar 2.5. Register CPU 8088

register akan terbagi menjadi 2 register yaitu : AH, AL, BH, BL, CH, CL, DH dan DL. Fungsi dari register-register ini adalah untuk pelaksanaan operasi-operasi aritmatik dan logika.

Pointer dan Index group terdiri atas 4 buah register 16 bit yaitu: SP (Stack Pointer) BP (Base Pointer), SI (Source Index), DI (Distination Index). Register-register ini hanya dapat dioperasikan untuk 16 bit. Fungsi dari register-register index dan pointer ini adalah untuk pembentukan memory effektif address (EA). Tabel 2.5. menunjukkan pengguanan data group register serta pointer dan index group register dalam instruksi.

Walaupun hanya terdiri atas 16 bit register, pointer dan index group ini mampu untuk melakukan addressing lebih dari 65.536 byete (64 kbyte) data yang dapat di address oleh 16 bit register. Kemampuan addressing dari CPU 8088 adalah 20 address yaitu 1.048.567 byte (Mbyte). Tetapi ada pula instruksi dari CPU 8088 yang hanya dilaksanakan untuk 16 bit address.

Cara yang dilakukan oleh CPU 8088 untuk mendapat 20 bit addreess dari 16 bit addreess adalah dengan menambahkan 16 bit offset address ke 16 bit segment address yang digeser ke kiri sebanyak 4 kali atau dengan kata lain segment address-nya dikalikan dengan 16 dan

Tabel 2.5. Operasi Register CPU 8088<sup>8)</sup>

| REGISTER | OPERASI                                                         |

|----------|-----------------------------------------------------------------|

| XA       | Perkalian Word, Pembagian Word, I/O                             |

| AL       | Perkalian Byte, Pembagian Byte, I/O                             |

| АН       | Ttranslasi, Aritmatik desimal<br>Perkalian Byte, Pembagian Byte |

| ВХ       | Translasi                                                       |

| CX       | Operasi string                                                  |

| CT       | Pergeseran Variabel dan Rotasi                                  |

| DX       | Perkalian Word, Pembagian Word, I/O                             |

| SP       | Operasi Stack                                                   |

| SI       | Operasi String                                                  |

| DI       | Operasi String                                                  |

baru ditambahkan dengan offset address. Dengan adanya segment maka address dari memory akan terdiri atas segment-segment masing-masing mempunyai kapasitasnya sebesar 64 Kbyte. Harga dari segment register biasa disebut sebagai base dan harga yang ditambahkan dengan segment address biasa disebut sebagai offset.

Segment register terdiri atas 4 buah register 16 bit yaitu :

- DS (Data Segment)

- CS (Code Segment)

- SS (Stack Segment)

<sup>8)</sup> Ibid, hal 36

## - ES (Exstra Segment)

Seperti diterangkan diatas fungsi segment register ini adalah untuk membentuk segment-segment sebesar 64 Kbyte di dalam batas daerah 1 Mbyte daerah memory. Didalam perangkat lunak empat buah segment register akan mempunyai fungsi sendiri-sendiri untuk penentuan addreess dari memory yang digunakan. Penggunaan masing-masing segment register ini dapat dilihat pada tabel 2.6.

Instruction Pointer Register merupakan register

16 bit yang berfungsi sebagai offset address dari lokasi

memory instruksi yang berikutnya pada harga base code

segment saat itu.

Flag register merupakan 16 bit register, tetapi hanya 9 bit yang digunakan. Dari 9 bit ini 6 bit merupakan status bit yang menunjukkan status dari hasil operasi aritmatika dan logika. Tiga bit merupakan control bit. Susunan bit dari flag register ini dapat dilihat pada gambar 2.6.

Berikut ini adalah penjelasan dari fungsi masingmasing bit dari Flag Register:

- AF (Auxiliary cary flag)

Bit ini akan di-set apabila dalam operasi aritmatik terdapat carry out, borrow, atau borrow

dari nible perhitungan desimal.

- CF (Carry Flag)

Tabel 2.6. Penggunaan Segment Register dan Offset<sup>9)</sup>

| TIPE REFERENSI<br>MEMORY               | BASE<br>SEGMENT | BASE SEGMENT ALTERNATIF | 0 | FFSET |

|----------------------------------------|-----------------|-------------------------|---|-------|

| Instruction Fetch                      | CS              | Tidak ada               |   | ΙP    |

| Operasi Stack                          | SS              | Tidak ada               |   | SP    |

| Variabel                               | DS              | CS, ES, SS              |   | EA    |

| String Source                          | DS              | CS, ES, SS              |   | SI    |

| String Disti-<br>nation                | ES              | Tidak ada               |   | DI    |

| BP dipakai<br>sebagai BASE<br>REGISTER | SS              | CS, DS, ES              |   | EA    |

Gambar 2.6. Flag Register CPU 8088

<sup>9)</sup> Ibid,hal.37

Bit ini akan di-set apabila terjadi carry out atau borrow pada high-order bit sebagai hasil operasi arimatik.

## - OF (Overflow Flag)

Bit ini akan di-set apabila terjadi overflow atau hasiloperasi aritmatika terlalu besar untuk daerah yang dituju.

#### - SF (Sign Flag)

Menunjukkan tanda dari bilangan hasil operasi aritmatik. Bila di-set maka tanda bilangan adalah negatif.

## - PF (Parity Flag)

Flag ini akan di-set apabila hasil operasi mempunyai jumlah bit yang berlogika satu atau genap.

## - **ZF** (Zero Flag)

Flag ini di-set apabila hasil operasi aritmatika nol.

#### - DF (Dercrement Flag)

Bit ini merupakan control bit, jika di-set maka operasi string akan melakukan proses pengurang secara otomatis dari address tertinggi ke address terendah. Jika bit nol, maka pada operasi string akan dilakukan penambahan secara otomatis.

#### - IF (Interupt flag)

Apabila control flag di-set, maka memungkinkan

CPU 8088 menerima external maskable interupt

- TF (trap Flag)

Merupakan control bit. Jika bit ini di-set maka CPU 8088 dalam mode single step. Akhir instruksi, interupt dibangkitkan otomatis.

#### II.3. METODA PENGALAMATAN

Metoda yang sering digunakan untuk men-decode suatu address sehingga dihasilkan sinyal pilih (CS signal) adalah metoda:

#### II.3.1 GATING

Gating adalah cara pengalamatan yang paling sederhana untuk mendecode suatu kombinasi address dengan menggunakan gate-gate logika seperti AND, OR dan NOT. Dengan metode gating ini setiap kombinasi address memerlukan satu rangkaian logika untuk mendapatkan satu sinyal pilih. Menurut pengalaman cara ini tidak banyak digunakan karena menjadi tidak efisien untuk sinyal pilih yang banyak. Namun dengan semakin meluasnya pemakaian PLD yang praktis, maka teknik pengalamatan gating banyak dipakai lagi.

#### II.3.2 DECODING

Cara yang paling mudah dan efisien un tuk decoding adalah dengan menggunakan dekoder. Dengan penggunaan decoder maka setiap n kombinasi address dapat diperoleh sebanyak 20 sinyal pilih, sehingga untuk sistem yang memerlukan sinyal pilih yang banyak biasanya dipakai cara decoding. Jika sinyal pilih yang merupakan output dari decoder dihubungkan ke chip select (C5) langsung suatu IC, maka disebut dengan partial decoding, sedangkan jika output decoder berikutnya sehingga diperoleh suatu susunan decoder yang bertingkat maka disebut dengan full decoding.

Ada beberapa macam decoder yang dapat digunakan dalam suatu sistem mikroprosessor untuk menentukan lokasi address dari memory atau pheriperal, salah satunya adalah IC decoder SN 74LS2138 yang mempunyai 3 buah input untuk kombinasi address-nya dan 8 buah output untuk menghasilkan sinyal pilih yang sesuai.

IC ini disebut 3 to 8 line decoder. Pada data sheet terlampir, 3 input tersebut adalah pin A, pin B, dan pin C dimana pin C adalah Most Significat Bit (MSB) dan pin A adalah Least Significat Bit (LSB), sedangkan ke 8 outputnya adalah YO sampai Y7. Jika pin-pin enable diberi sinyal yang sesuai dengan tabel kebenarannya (G1

Gambar 2.7. IC Decoder 74LS138

tinggi G2A dan G2B kedua-duanya rendah), maka akan di peroleh kombinasi input dari bit-bit address akan menghasilkan salah satu pin output yang sesuai. Gambar 2.7 membantu untuk mengenal IC decoder.

#### II.4. BUFFER

Untuk melayani perangkat memory atau I/O dari suatu sistem mikroprosessor, CPU memerlukan komponen tambahan buffer untuk menambah kemampuan pembebanan pada fan out-nya. Buffer-buffer ini diperlukan jika dibebani melebihi fan out. Akibat dari pembebanan melebihi fan out adalah level tegangan pada pin-pin bus yang bersangkutan dapat turun (untuk level tinggi), atau naik (untuk level rendah) melampaui batas level Margin-nya. Apabila batas level Margin telah dilamapaui akan mengakibatkan CPU memberikan informasi yang tidak benar pada seluruh sistem. Untuk menghindari kesalahan

Gambar 2.8 Buffer Address Bus

informasi dari kondisi tak menentu level tegangan, maka harus ditambahkan buffer pada sistem busnya.

Pemakaian buffer disini tidak sekedar menambah kemampuan fan out saja, namun harus diperhitungkan juga waktu tunda akibat dari pemasangan komponen buffer tersebut. waktu tunda dari komponen buffer tesebut harus kecil, dan sekecil mungkin perbedaaan waktu tunda antara bit yang satu dengan bit yang lain dalam satu bus.

Buffer yang akan digunakan harus disesuaikan dengan kebutuhannya dalam sistem bus. Yang perlu diper-

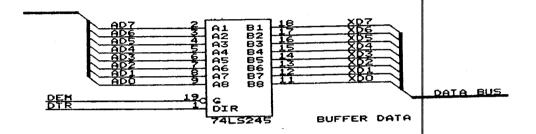

hatikan bila menggunakan buffer bidirectional adalah mengenai control logic yang mengatur arah data yang akan dibuffer. Gambar 2.8 menunjukkan buffer address bus dengan IC74LS244 dan 74LS373, sedangkan pada gambar 2.9 menunjukan buffer data bus menggunakan IC 74LS245.

Gambar 2.9 Buffer Data Bus

#### II.5. MEMORI

Bagian yang sangat penting dalam sistem mikroprosessor dinamakan memory. Memory merupakan tempat penyimpanan informasai yang dapat berupa data atau instruksi. Informasi dalam memori ada yang bersifat sementara (volatile) atau yang bersifat permanen (non volatile). Memori sendiri menurut fungsi tersebut diatas terdiri dari beberapa jenis, yaitu:

- ROM (Read Only Memori)

- RAM (Random Access Memori).

## II.5.1. READ ONLY MEMORY (ROM)

Suatu sistem mikroprosesor memer lukan suatu memory yang dapat menyimpan data untuk selamanya (non volatile), dimana data yang terdapat pada memory tersebut tidak akan hilang bila power supply dari sistem dimatikan. Dikatakan ROM karena informasi yang ada didalamnya hanya dapat dibaca saja dan tidak capat diubah, sehingga ROM berguna dalam suatu sistem karena dapat meng-inisialisasi semua pheriperal perangkat keras (hardware) pada saat pertama kali sistem dinyalakan.

Pada ROM data atau informasi dimasukkan dalam memory chip oleh user dengan suatu alat yang dapat memberikan pulsa tegangan yang cukup tinggi kedalam sel-sel memory chip. Pada ROM dan PROM informasi yang telah disimpan masih dapat dihapus dengan memberikan sinar ultra violet dengan intensitas tertentu pada jendela dari IC pada PROM. jenis ROM yang umum dipakai adalah EPROM, dangan kapasitas penyimpanannya mulai dari 2 KByte hingga 64 KByte.

# II.5.1.1. KARAKTERISTIK ROM

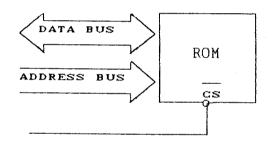

ROM hanya dapat dibaca datanya oleh CPU saja (READ ONLY), dengan memberikan alamat dari ROM tersebut.

Blok diagram dari ROM ditunjukan pada gambar 2.10.

Banyak data yang dapat disimpan dalam suatu ROM, biasanya ditulis 2048 x 8 untuk 2 kilo byyte, atau 4096 x 8 untuk 4 kilo byte. Deretan angka vang pertama misalnya 2048, menunjukkan jumlah lokasi address yang dapat disimpan dalam ROM sedangkan deretan yang misalnya 8 menunjukkan jumlah byte data pararel dapat diterima dari ROM untuk setiap lokasi address.

Gambar 2.10 Blok Diagram  $ROM^{10}$ )

Untuk lokasi address sejumlah 2048 lokasi dibutuhkan 11 jalur address, karena kombinasi biner sejumlah 2048 atau dua pangkat sebelas.

Dalam suatu ROM terdapat suatu kaki yang disebut Chip Select (CS). Fungsi dari CS ini adalah untuk me-aktifkan data output dari ROM. Dengan membuat CS ini aktif, data memory akan dikeluarkan pada output data bus

<sup>10)</sup> Ibid, hal.4

sesuai dengan lokasi address yang diinputkan pada ROM.

Jika CS ini tidak aktif, maka semua data output dalam keadaan tri-state (high impedance state).

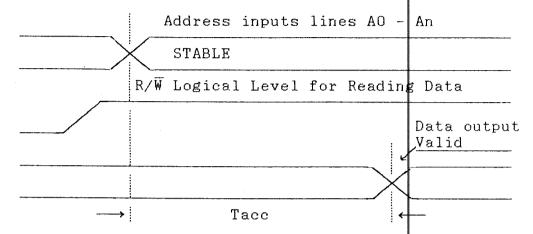

#### II.5.1.2. MEMBACA DATA ROM

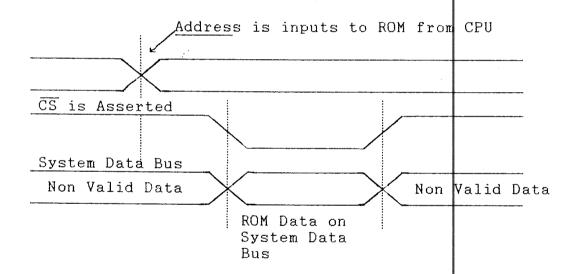

Urutan sinyal yang diperlukan untuk membaca data dari ROM adalah sebagai berikut:

1. CPU memberikan input address kepada pin-pin ROM sesuai dengan lokasi yang akan dibaca.

Gambar 2.11. Diagram Waktu Pembacaan Data ROM

2. CPU menunggu untuk selang waktu tertentu berkisar antara 100 - 840 nS. Selang waktu ini diperlukan ROM untuk men-decode addres yang diterima dan menunggu data dari lokasi memori yang dituju menca-

pai data output line.

- 3. Sinyal CS diaktifkan, maka data akan dikeluarkan oleh ROM pada data bus.

- 4. Kemudian sinyal CS tidak diaktifkan untuk me niadakan data dari EPROM pada data bus, sehingga line data pada EPROM pada keadaan tri-state (impedansi tinggi).

Untuk sinyal sinyal tersebut diatas selalu terjadi setiap saat CPU membaca ROM. Diagram waktu untuk urutan urutan sinyal tersebut ditunjukan dalam gambar 2.11.

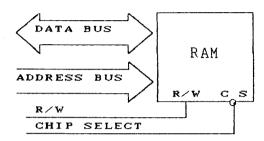

## II.5.2. RANDOM ACCESS MEMORI (RAMD

RAM merupakan sistem memori yang dapat menyimpan data hanya untuk sementara (power supply mati data akan hilang). Dinamakan Random Access Memory (RAM) karena lokasi manapun dapat dicapai secara langsung dengan menempatkan inputnya.

Pada RAM terdapat parameter Read Access Time (menentukan kecepatan RAM) yaitu waktu yang diperlukan oleh data untuk menjadi valid. Parameter lain adalah write access time yaitu waktu yang diperlukan sesudah address bus yang diberikan pada input valid sebelum pulsa diberikan.

Ada dua jenis RAM yang dapat digunakan oleh CPU untuk menyimpan data, yaitu:

- a. Static Random Acess Memory (SRAM)

- b. Dynamic Random Acess Memory (DRAM)

SRAM dapat menyimpan data selama tegan gan supply tidak diputuskan sedangkan DRAM harus diteri Refresh cycle agar informasi dapat dipertahankan .

#### II.5.2.1. STATIC RANDOM ACESS MEMORY (SRAMD

SRAM adalah RAM yang dapat mengingat informasi tersebut tanpa perlu me-refresh informasi secara periodik. Selama sumber daya listrik bekerja, semua informasi yang disimpan dalam SRAM dapat diingat dengan baik. Jadi pada Statik RAM hanya diperlukan dua hal saja, yaitu Read dan Write.

#### II.5.2.2. DINAMIC RANDOM ACESS MEMORY (DRAM)

Perbedaan pokok antara DRAM dan SRAM adalah diperlukannya sinyal "Refresh" pada DRAM secara periodik untuk mempertahankan informasi yang disimpan agar jangan hilang. Oleh karena itu pada DRAM selain Read dan Write cycle juga diperlukan refreshing cycle.

Dalam pemakaiannya SRAM lebih praktis dibanding

DRAM karena tidak diperlukan rangkaian refresh. Namun demikian dalam segi pembuatannya DRAM lebih mudah di-implementasikan, selain itu keuntungan yang lain adalah

Gambar 2.12. Blok Diagram RAM<sup>11</sup>

bentuk kemasan yang lebih kecil dan dissipasi daya yang cukup rendah. Hal inilah yang menyebabkan DRAM kadang-kadang dipertimbangkan untuk dipakai dalam sistem mikro-prosessor yang memerlukan memori dengan kapasitas besar.

#### II.5.2.3. MEMBACA DATA RAM

Urut-urutan sinyal yang dipeerlukan untuk membaca data dari RAM sebagai berikut:

Memory memerlukan address yang menentukan lokasi tertentu. Rangkaian decoder ke RAM tersebut mengaktifkan CS dari RAM.

<sup>11)</sup> Ibid, hal. 28

Tacc: Time required for data to stable at the memory data output lines during a memory read operation

## Gambar 2.13 Diagram Waktu Baca Data RAM.

- 2. Sinyal MEMR (memory read) menjadi aktif dan memory langsung menerima sinyal ini.

- 3. Kemudian sistem menunggu dalam selang waktu tertentu (Read Acces Time) sampai rangkaian dalam RAM stabil.

- 4. Setelah Access Time, data akan muncul pada data bus, dan data dapat dietrima oleh CPU, Jika CPU terlalu cepat mengaktifkan sinyal CS (tidak menunggu Read Access Time), atau lambat mengaktifkan sinyal CS, maka CPU akan mendapat data yang salah (tidak valid).

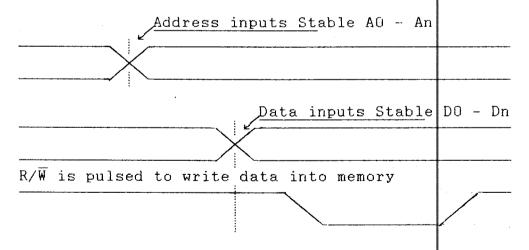

#### II.5.2.4. MENULIS DATA RAM

Diagram waktu penulisan data ke RAM, seperti ditunjukan dalam gambar 2.14. Dimana proses penulisannya sebagai berikut:

- 1. Address dari data yang akan ditulis dimasukan ke address dari memory melalui address bus sesuai dengan lokasi yang ditentukan. Sebagian address bus dan control bus menuju rangkaian decoder untuk memberikan sinyal pilih memory pada CS.

- 2. Data yang akan ditulis ke memori diletakkan pada D7 - D0 melalui data bus.

- 3. CPU menunggu untuk selang waktu tertentu (Write Access Time), untuk memberi kesempatan rangkaian decoder didalam RAM stabil.

Gambar 2.14 Diagram Waktu Tulis Data RAM.

4. Setelah Write Access Time, maka sinyal Write diaktifkan sehingga data disimpan pada sel RAM.

#### II.6. UNIT INPUT OUTPUT

Unit input/output merupakan unit dimana suatu sistem mikroprosesor dapat berkomunikasi dengan perangkat pheriperal diluar sistem tersebut. Unit input berfungsi menerima informasi dari luar kemudian menerjemahkannya dalam bahasa sinyal digital yang dimengerti oleh CPU, sehingga informasi dapat diolah dan diprosees.

Unit output berfungsi untuk menerjemahkan informasi yang telah diolah dan diproses tersebut kedalam bahasa yang dimengerti oleh pemakai. Dengan demikian unit input dan output merupakan sarana komunikasi pemakai dengan sistem.

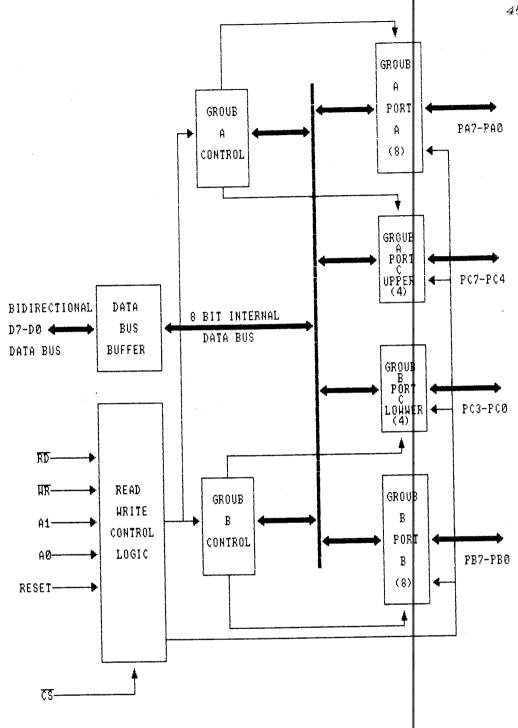

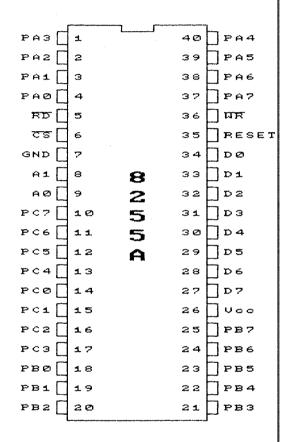

## II.6.1. PROGRAMABLE PERIPHERAL INTERFACE (PPI) 8255

Programable Peripheral Interface 8255 dirancang sebagai interface dalam sistem mikroprosesor yang dikemas dalam bentuk 40 pin Dual In Line Package (DIP) yang termasuk jenis Large Scale Integration (LSI).

Gambar 2.15 menunjukan diagram blok dari PPI

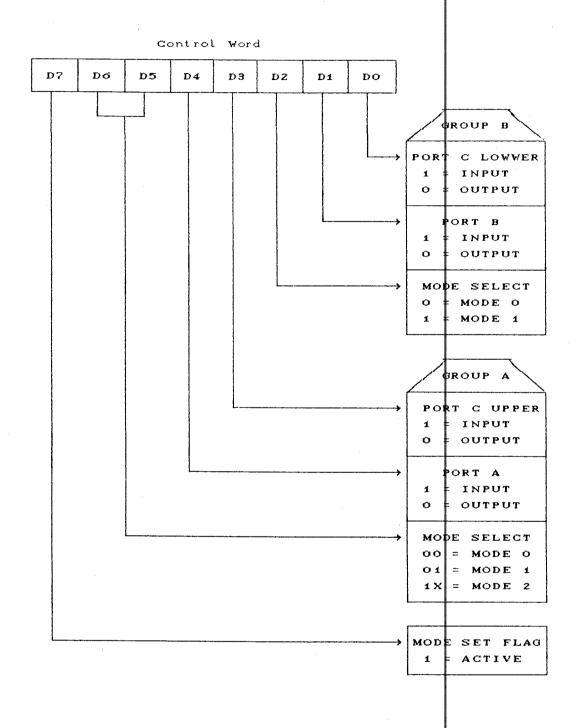

8255. Pada gambar tersebut terlihat dua kelompok besar yang disebut kelompok kendali A dan kelompok kendali B. Kedua kelompok kendali tersebut mengendalikan empat kanal. Tiga kanal merupakan I/O port, dengan masing-masing berukuran 1 byte dan sebuah kanal yang lain merupakan control word atau control register yang berukuran 1 byte.

Pengendalian kelompok tersebut diatur bleh kanal ke-empat yaitu control word atau control register. Tugas kanal ke-empat control word atau control register ini memformat kanal-kanal yang lain sebagai port input atau sebagai port output. Kanal ke-empat control word atau control register dalam bekerjanya mendapatkan input dari mikroprosessor melalui sinyal-sinyal RD; WR; AO; A1; RESET; D7 - D0; dan IO/M (dengan pengalamatan decoder menghasilkan sinyal pilih CS)

Diantara dua kelompok kendali tersebut bisa bekerja secara mandiri (pada mode 0) atau bisa juga bekerja sama (pada mode 2). Dari ke-tiga kanal I/O port tersebut ada satu kanal yang posisinya berada dalam dua kelompok kendali tersebut. Untuk itu empat bit orde tinggi ikut kelompok kendali A dan empat bit orde rendah ikut kelompok kendali B. Sehingga pada kanal yang satu ini dalam satu byte bisa terpecah menjadi empat bit input dan empat bit output.

2.15<sup>12)</sup> Diagram Blok PPI **8**255 Gambar

<sup>12)</sup> Intel Corporation, Microsystem Components Handbook (Santa Clara: Intel Corporation, 1984), p 6-358.

Tiga kanal I/O port dalam kedua kelompok tersebutt:

- Port A (PAO PA7)

- PortB (PBO PB7)

- Port C Lower (PCO PC3)

- Port C Upper (PC4 PC7)

Kelompok A mengontrol fungsi dari port A dan port C upper, sedang kelompok B mengontrol fungsi dari port B dan port C lower.

Semua bagian dalam PPI 8255 tersebut dihubungkan dengan internal data bus, dan melalui internal data bus inilah data dikirim atau diterima oleh setiap port.

Port-port tersebut dapat digunakan dengan 3 mode, yaitu:

- Mode O (Basic Input/output)

- Mode 1 (Strobed input/output)

- Mode 2 (bidirectional bus)

Adapun pengaturan mode tersebut melalui control word data 8 bit yang diperlihatkan pada gambar 2.16.

#### II.6.2 FUNGSI PIN PPI 8255

Fungsi dari masing-masing pin PPI 8255 dapat dijelaskan sebagai berikut:

#### 1. DataBus (DO-D7):

Digunakan untuk input/output dari peralatan luar, dimana semua informasi diterima dan dikirim mela

Gambar 2.16 Register Control World

lui 8 bit data.

#### 2. Chip Select (CS):

Chip Select ini digunakan untuk mengaktifkan chip PPI 8255. Bila mendapat logika "O", CFU dapat mengirim data atau menerima data dari PFI 8255.

## 3. Read (RD):

Bila RD dan CS juga mendapat logika "O", maka data output dari PPI 8255 dapat dikeluarkan pada sistem data bus, dan siap dibaca oleh CPU.

## 4. Write (WR):

Bila WR dan CS juga mendapat logika "0", maka data dari CPU dapat dikirim ke PPI 8255 melalui data bus.

### 5. Address Input (AO - A1):

Kombinasi dari kedua address input ini menentukan register mana dari PPI 8255 yang akan menerima atau mengirim data dari atau ke CPU

## 6. Reset:

Fungsi dari pin ini adalah untuk mereset PPI 8255 dengan memberikan input logika "1". Pada saat reset ini semua I/O port diset dalam mode input.

### 7. Port A (PAO - PA7):

Pin ini digunakan sebagai delapan bit input/output port untuk berhubungan dengan peralatan luar.

#### 8. Port B (PBO - PB7):

Pin ini fungsinya sama dengan port A, tetapi kedua port tersebut saling bebas satu dengan lainnya.

## 9. Port C (PC0 - PC7):

Pin ini fungsinya sama dengan port B, tetapi pada

Gambar 2.17 $^{f3}$ Konfigurasi Pin-pin PPI 8255

<sup>13)</sup> Ibid, hal.116

port C ini dapat dibagi menjadi 2 kelompok yaitu Port C Lower (PCO - PC3) dan Port C Upper (PC4 - PC7) masing-masing 4 bit yang digunakan untuk mengontrol peralatan luar yang berhubungan dengan PPI 8255.

Sedang konfigurasi dari pin-pin PPI 8255 dapat dilihat pada gambar 2.17. Seperti diketahui bahwa PPI 8255 mempunyai dua buah address input, AO dan A1 untuk memilih salah satu dari empat buah register yang dimilikinya. Umumnya dua address input ini dihubungkan ke AO dan A1 dari CPU 8088. CS input line PPI 8255 digunakan untuk menempatkan PPI 8255 ke addres I/O yang direncanakan. Misalnya I/O addres direncanakan boleh terletak dimana saja diantara address OOH - 3FH: yaitu

Tabel 2.7 Read Write Register

| RD                              | WR                                   | A1                              | AO                              | NAMA REGISTER                                                                                                                                  |  |

|---------------------------------|--------------------------------------|---------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1 | 1<br>0<br>1<br>0<br>1<br>0<br>1 | Write port A (data) Read port A (data) Write port B (data) Read port B (data) Write port C (data) Read port C (data) Write Control Word Ilegal |  |

A7 A6 A5 A4 A3 A2 A1 A0. Tabel 2.7 berikut adalah defenisi read dan write regiter dari PPI 8255

#### II.7. SISTEM KOMUNIKASI DATA

Kerja sama antara sistem komputer dar atau antara komputer dengan suatua alat yang dikendalikannya, membutuhkan suatu sistem komunikasi data. Umumnya pada perangkat komputer itu sendiri semua data bekerja secara paralel melalui saluran data bus.

Pada prinsipnya transfer data dapat dilakukan dengan menggunakan salah satu dari 2 cara berikut:

- 1. Transfer data paralel

- 2. Transfer data serial

## II.7.1. TRANSFER DATA PARALEL

Transfer data bit paralel sering disebut transfer data paralel, yaitu bit-bit data yang bersangkutan dikirimkan sekaligus dalam waktu bersamaan. Jika yang dikirimkan 8 bit sekaligus disebut bit parallel, sedangkan apabiala yang dikirimkan 16 bit sekaligus disebut word paralel. Kelebihan dengan transfer data paralel adalah efesiensi dalam waktu, namun kendalanya adalah keterbatasan dalam jangkauan (jarak).

Transfer data paralel memerlukan jumlah kawat saluran minimal sejumlah bit yang dikirimkan. Transfer data paralel sederhana dalam software maupun hardware. Panjang kawat yang dipakai untuk komunikasi transfer data paralel umumnya tidak lebih dari satu meter, misalnya Centronic Paralel Interface antara komputer dengan printer atau komputer dengan ploter.

#### II.7.2. TRANSFER DATA SERIAL

Transfer data serial, tiap-tiap bit dikirimkan dengan selang waktu tertentu yang tergantung pada kecepatan pengiriman bit data serial tersebut yang dinyatakan dalam baud rate. Transfer data bit serial menempati bidang yang penggunaannya khas, terutama dapat digunakan untuk jarak lokal didalam ruangan, ataupun untuk jarak jauh dengan dilengkapi modem. 14)

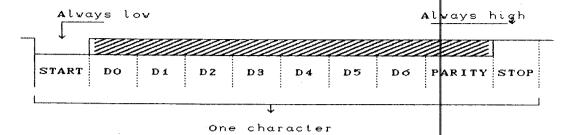

Dalam pengiriman data serial harus ada sinkronisasi atau penyesuian antara pengirim dan penerima agar data yang dikirmkan ditafsirkan secara tepat dan benar oleh penerima. Berdasarkan cara sinkronisasi dikenal tiga mode transmisi serial yaitu:

- Transmisi Asinkron (Asynchronous)

Transmisi Asinkron digunakan bila pengiriman data

dilakukan satu karakter setiap kali. Antara satu

Hartono Partoharsodjo. Tuntunan Praktis Pemrograman Bahasa Asembly, PT. Elex Media Komputindo, Jakarta 1990, hal. 548.

Gambar 2.18 Format Bit Serial Asinkron

karakter dengan yang lainnya tidak ada waktu an tara yang tetap. Akibatnya setiap kali menerima data harus melakukan sinkronisasi supaya data dapat ditrima dengan benar. Dengan demikian penerima harus mengetahui mulainya bit pertama dari suatu data dengan stop atau akhir dari suatu data atau stop bit.

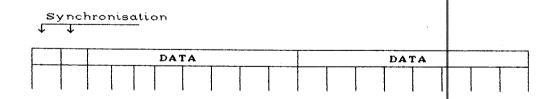

- Transmisi Sinkron (Synchronous)

Digunakan untuk transmisi kecepatan tinggi, yang ditransmisikan dalam satu blok data. Dalam sistem ini baik pengirim maupun penerima bekerja bersama-sama dan sinkronisasi dilakukan setiap se-

Gambar 2.19 Format Bit Serial Sinkron

kian ribu bit data. Sinkronisasi terjadi dengan mengirimkan pola data tertentu antara pengirim dan penerima. Pola data tertentu ini disebut karakter sinkronisasi (synchroniztion character)

- Transmisi Isokron (Isyochronous)

Transmisi ini merupakan kombinasi dari asinkron dan sinkron. Tiap karakter didahului dengan start bit dan diakhiri dengan stop bit. Tetapi pengirim dan penerima disinkronisasi sebelum karakter tersebut dikirim atau diterima. Perioda tanpa transmisi terdiri atas satu atau lebih karakter. Sinkronisasi dilakukan sebesar satuan pewaktuan.

# II.7.3. METODA DAN STANDAR TRANSMISI SERIAL ASINKRON

Pada dasarnya transmisi ini mempunyai dua macamaturan atau protokol perangkat keras, yaitu:

#### II.7.3.1. CURRENT LOOP 20 mA

Merupakan sistem lama dan menggunakan arus, yaitu adanya arus yang mengalir menunjukan keadaan idle atau istirahat. Pengiriman informasi terjadi bila arus berubah besarnya. Arus minimum sebesar 18 mA harus ada dan arus maksimum yang diperbolehkan besarnya 25 mA untuk

menjaga agar disipasi tidak berlebihan. Pada mulanya sistem ini digunakan untuk mentransfer data biner serial teleprinter.

Keuntungan sistem ini adalah sederhana, ekonomis dan murah. Kerugiannya, noise filtering sukar dan tidak ada pembakuan tegangan, serta membangkitkan cros-talk kalau digunakan kabel yang panjang.

### II.7.3.2. RS-232C

Semua sinyal listrik yang disalurkan melalui media tranmisi akan bertambah lemah karena adanya hambatan, kapasitansi serta induksi media. Akibatnya sinyal informasi dapat terganggu oleh derau dan terdapat kemungkinan sukar membedakan antara keduanya. Penyaluran informasi yang jaraknya jauh membutuhkan penguatan atau cara lain supaya informasi dapat tiba ditempat tujuan.

Guna mencapai tujuan ini digunakan gelombang pembawa yang memodulasi sinyal informasi dengan gelombang, dikenal sebagai modem. Agar peralatan komunikasi data dapat saling berhubungan dibuat suatu ketentuan baku. Data Terminal Ready (DTE) dan Data Communication Equipment (DCE) atau juga menghubungkan antara dua Data Terminal Equipment seperti komunikasi antar komputer yang melakukan pertukaran data secara serial dengan

sinyal biner dapat menggunakan standar RS-232C yang dibuat oleh EIA (Electrical Industry Assocition).

Standar RS-232C berisikan karakteristik sinyal listrik, karakteristik mekanik dan cara operasi rangkai- an fungsionalnya, dengan penjabaran sebagai berikut:

## 1. Karakteristik Sinyal listrik

- Tegangan rangkaian terbuka tidak beleh lebih dari 25V.

- Keadaan logika "1" (MARK) ditandai dengan tegangan lebih negatip dari -3V (-5V s/d -15V).

- Keadaan logika "O" (SPACE) ditandai dengan tegangan lebih positip dari +3V (+5V s/d +15V).

- Hambatan keluaran DC harus lebih kecil dari  $7K\Omega$  (tegangan 3V s/d 25V), dan lebih besar dari  $3K\Omega$  (tegangan kurang dari 25V).

- Slew Rate harus lebih kecil dari 30  $V/\mu$ S. Waktu untuk melewati daerah peralihan -3V s/d +3V tidak boleh lebih dari 1mS.

## 2. Karakteristik Mekanik

- Karakteristik mekanik untuk antar interface baku ini juga ditentukan yaitu penggunaan konektor DB 25P dan DB 25S. Tiap kontak dari konektor ini berasal dari rangkaian fungsional tertentu.

- 3. Cara Operasi rangkaian Fungsional

## - Protective Ground (AA)

Pin no 1 ini dihubungkan secara listrik dengan frame dari peralatan yang kemudian dapat disambungkan ketanah (external ground) jika diperlukan.

## - Signal Ground (AB)

Pin no 7 ini membentuk potensial acuan untuk semua rangkaian kecuali protective ground.

## - Transmitted Data/TXD (BA)

Pin no 2 merupakan sinyal yang dibangkitkan oleh DTE untuk diberikan pada DCE guna disalur kan melalui saluran komunikasi ke tujuannya. Ketentuan RS-232C meminta agar DTE harus dalam keadaan MARK saat tidak ada data yang dikrimkan atau pada interval antar karakter. Transmisi melalui saluran komunikasi hanya dilaksanakan DTE bila keadaan SPACE ditemui pada rangkaian: RTS, CTS dan DTR.

# - Received Data/RXD (BB)

Pada pin no 3 ini sinyal data yang dibangkitkan oleh DCE dalam sinyal yang diterima oleh remote station. RS-232C menghendaki sinyal ini harus dalam keadaan MARK bila sinyal carier detect dalam keadaan off.

- Request To send/RTS (CA)

Pada pin no 4 ini sinyal ini mengendalikan DCE lokal bagian transmit guna menyalurkan data. Keadaan on menyebabkan rangkaian DCE siap mengirimkan data. DTE kalau akan mengirimkan data, akan membuat RTS on. Untuk menyatakan DCE telah siap, rangkaian CTS menjadi on, sehingga DTE dapat mengirimkan data melalu. Transmitted Data.

- Clear To Send/CTS (CB)

- Pada pin 5 ini menyatakan sinyal DCE siap menerima data melalui saluran komunikasi. Keadaan off (MARK) pada rangkaian untuk menyatakan DTE tidak mengirimkan data.

- Data Set Ready/DSR (CC)

Pada pin no 5 ini digunakan untuk menyatakan status dari modem yang tersambung pada DCE.

Keadaan on menyatakan bahwa modem telah tersambung pada saluran, dan DCE lokal siap bertukar sinyal kendali dengan DTE untuk memulai

- Carrier Detect/CD (CF)

pertukaran data.

Pada pin no 8 ini status on menyatakan bahwa saluran dalam kondisi baik, dan dapat menerima maupun mengirimkan data. Status off menyatakan bahwa saluran dalam kondisi kurang baik sehing-

ga tidak dapat melakukan modulasi. Pada keadaan ini rangkaian RXD akan ditahan pada keadaan MARK.

- Data Terminal Ready?DTR (CD)Pada pin no 20 sinyal ini mengendalikan DCE lokal bagian transmit guna menyalurkan data. Kesdaan on menyebabkan rangkaian DCE siap mengirimkan data. DTE kalau akan mengirimkan data, akan membuat DTR on. Untuk menyatakan DCE telah siap, rangkaian DSR menjadi on, sehingga DTE dapat mengirimkan data melalui Transmitted Data.

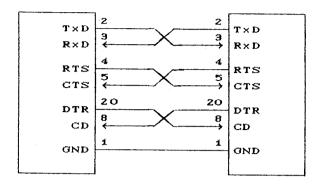

#### II.7.3.3. KONFIGURASI HUBUNGAN RS-232C

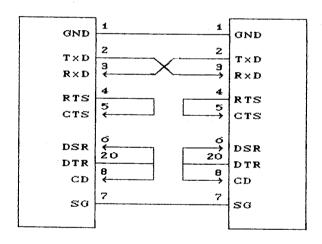

Hubungan komputer yang jaraknya dekat tidak memerlukan modem, tetapi tetap mengikuti standar RS-232C. Hubungan ini disebut null modem atau cross-over seperti gambar 2.20.

Bila dihubungkan komputer dengan peralatan lain, dapat digunakan sebagian, seluruh atau tanpa sinyal handshake seperti ditunjukan pada gambar 2.21.

Gambar 2.20 Hubungan RS-232C Null Modem

Gambar 2.21 Hubungan RS-232C Tanpa Handshake

## BAB III PERENCANAAN SISTEM

#### III.1. PERENCANAAN PERANGKAT KERAS

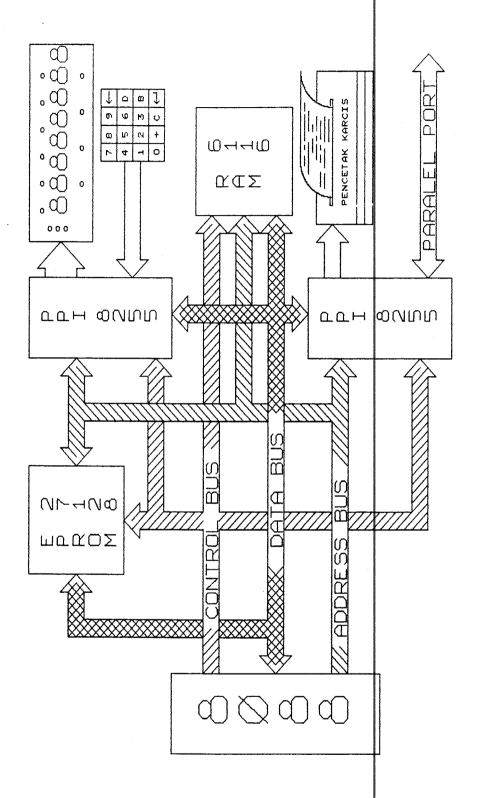

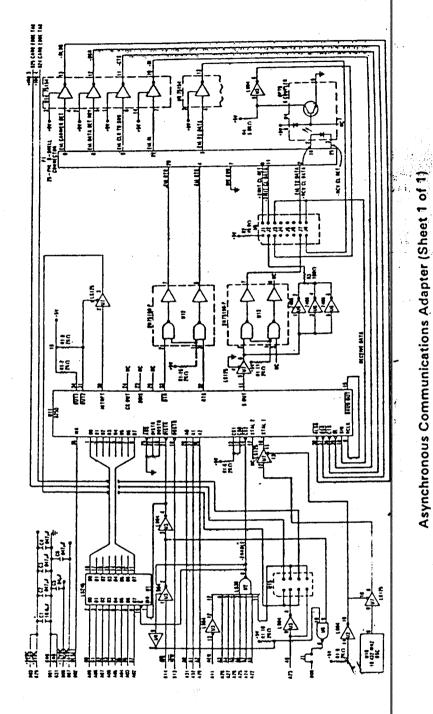

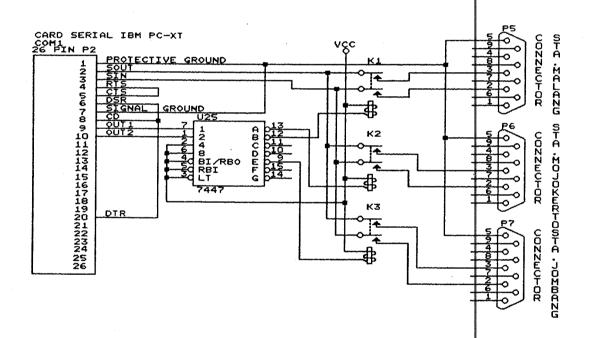

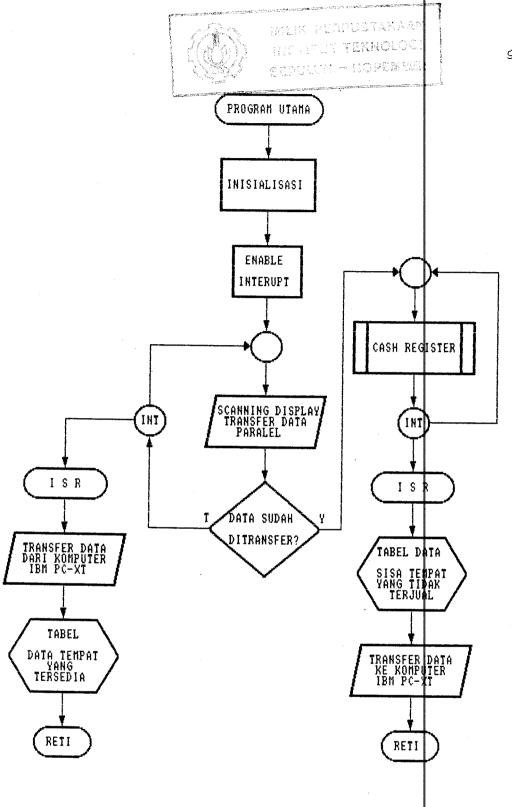

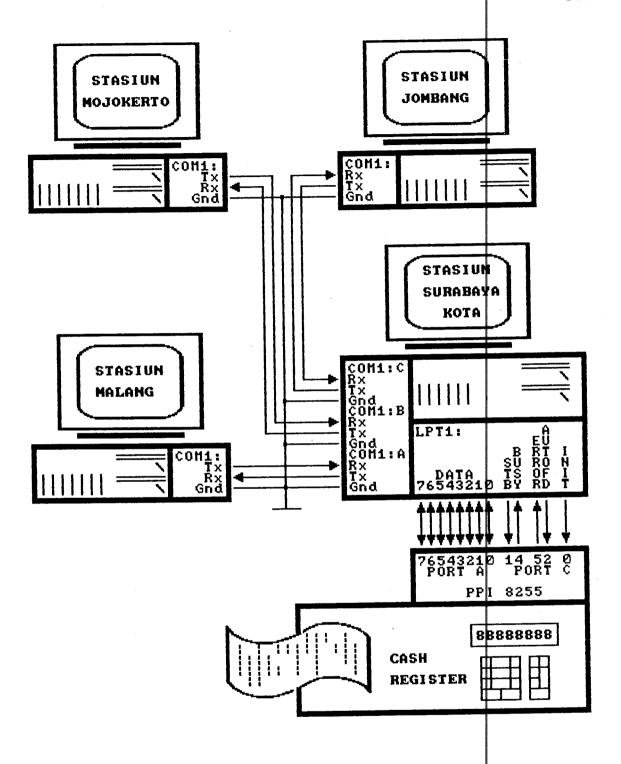

Untuk dapat membentuk suatu sistem dengan hasil yang optimal maka perlu dilakukan perencanaan komponen dasar maupun komponen pendukungnya. Pada bab ini dibahas perencanaan CPU 8088 U2 yang dioperasikan sebagai Minimum (MN/MX dihubungkan Vcc), serta komp|nen-komponen pendukungnya. Dimana pada tugas akhir ini sistem mikroprosessor digunakan untuk mengatur kalkulasi uang, memilih dan mencetak nomor tempat duduk pada karcis kereta api, serta menerima transfer data baralel dari komputer. Sebagai komunikasi data tempat duduk stasiun penegendali dengan tiga stasiun cabang dibuat dengan komunikasi data serial yang diharapkan mempunyai jangkauan yang lebih jauh. Untuk itu dalam bab dibahas cara pengembangan COM1.

Untuk memperjelas sistem yang akan dibuat, diperlihatkan blok seperti yang ditunjukkan pada gambar 3.1. Pada sub bab ini akan diuraikan perencanaan dari masing-masing komponen pendukung tersebut.

Gambar 3.1 Blok Diagram Rencana Sistem

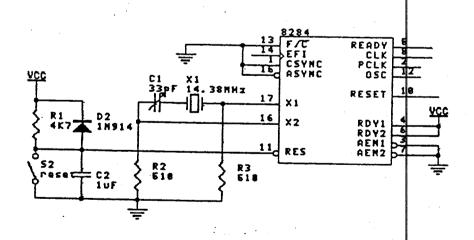

#### III.1.1. RANGKAIAN CLOCK

Sinkronisasi operasi internal dan eksternal CPU 8088 didukung oleh sinyal CLK IC 8284 (U1). Gambar 3.2 memperlihatkan konfigurasi pin IC 8284. Sinyal clock output pada PCLK selalu setengah dari frekwensi CLK tergantung dari kristal yang dipasang. Sedangkan output OSC tiga kali lipat frekwensi output CLK. Output dari clock-clock ini kompatibel dengan level TTL.

|    | 8284  |       |                                                  |

|----|-------|-------|--------------------------------------------------|

| 13 | FIC   | READY | <u> </u>                                         |

|    | EFI   | CLK   | <del>                                     </del> |

| 15 | CSYNC | PCLK  | 17                                               |

|    | ASYNE | 0 S C |                                                  |

|    |       | RESET | 18                                               |

| 17 | X1    | KESEI |                                                  |

| 16 | X2    | 22114 | 4                                                |

|    | X.Z   | RDY1  | <del>-</del>                                     |

|    |       | RDY2  | <del></del>                                      |

| 11 |       | AENI  | D                                                |

| q  | RES   | AEN2  | þ                                                |

Gambar 3.2 Konfigurasi IC 8284

Dalam sistem clock untuk tugas akhir ini adalah 4,77 MHz DC 33 % digunakan cristal 14,31818 MHz diseri dengan capasitor variabel C1 33 pF dihubungkan pada pin X1 dan X2 dari 8284. Untuk kestabilan sistem clock yang dibuat, dipakai R2 dan R3 yang besarnya 510  $\Omega$  dipasang pada input kristal dan groundkan.

Pin-pin READY, CLK, dan RESET masing di-